### 박 사 학 위 논 문

# 실리콘 기반 무선통신 및 센싱용

# RF 송수신기 전단부 설계연구

## 지도교수 박 정 동

# 동국대학교 대학원 전자전기공학과

남 효 현

2020

Dissertation for the degree of Doctor of Engineering

# Silicon-based RF Transceiver front-end Designs for Wireless Communication and Sensing Applications

**Advisor: Professor Jung-Dong Park**

Hyohyun Nam

Department of Electrical and Electronic Engineering Graduate School Dongguk University 2020

### 박사 학위 논문

실리콘 기반 무선통신 및 센싱용

RF 송수신기 전단부 설계연구

남 현 ब्रे

지도교수 박 정 동

이 논문을 박사학위 논문으로 제출함

2020년6월

남효현의 공학 박사학위 논문을 인준함

2020년7월

| 위육 | 신장 | <u>최</u> | 한 | <u>호</u> (인)  |

|----|----|----------|---|---------------|

| 위  | 원  | <u>김</u> | 민 | <u>성 (</u> 인) |

| 위  | 원  | <u>신</u> | 창 | <u> 환</u> (인) |

| 위  | 원  | <u>한</u> | 재 | <u>덕</u> (인)  |

| 위  | 원  | 박        | 정 | <u>동</u> (인)  |

동국대학교 대학원

Dissertation for the degree of Doctor of Engineering

# Silicon-based RF Transceiver front-end Designs for Wireless Communication and Sensing Applications

by

Hyohyun Nam

Advisor: Professor Jung-Dong Park

| Date of submission | .1 | 2020/06 |

|--------------------|----|---------|

| Date of approval   | +  | 2020/07 |

| Approved by:     | i la |

|------------------|------------------------------------------|

| Chairman         | : Professor Han Ho Choi Signi            |

| Committee member | : Professor Min-Sung Kim                 |

| Committee member | : Professor Changhwan Shin (Sign)        |

| Committee member | : Professor Jaeduck Han (Sign)           |

| Committee member | : Professor Jung-Dong Park Sign          |

Department of Electrical and Electronic Engineering

Graduate School Dongguk University 2020

### ACKNOWLEDGEMENTS

First of all, I would like to thank my advisor, professor Jung-Dong Park, for his guidance and encouragement during my study at Dongguk University. Due to his indepth experience and visionary ideas, I have acquired the fundamental of RF integrated circuit design. I am extremely grateful for his kind technological and personal assistance and guidance in making the work possible.

I would also like to thank professor Min-Sung Kim, professor Changhwan Shin, and professor Jaeduk Han for agreeing to be on my dissertation committee, and professor Han Ho Choi for serving as the chair of my committee. Their comments and feedbacks have kept me on the right track.

I would like to thank MEIC Lab. members, Van-Son, Jeong-Moon, Van-Viet, Young Joe, Chen, Tae-Wha, Hyeon-Seok, Jun-Hee, Van-Du, and Hyeon-Hee. It was a pleasure to work with them as a lab member.

Last and most importantly, none of this would have been possible without support, motivation, patience and affection from my family and wife Hyejun Moon. This study would never have come to be without them.

### ABSTRACT

Owing to the rapid development of wireless communication and sensing technology, it is necessary to design a transceiver which is compatible with existing system as well as new system standards in a single chip with various functions. The design of transceivers with the state-of-the-arts performance in communication and sensing applications should satisfy numerous types of the required specifications such as broadband operation, high linearity, miniaturization, low power consumption, and low cost. Recently, due to the aggressive development of silicon (i.e., CMOS and SiGe BiCMOS) process technology, it is possible to design silicon-based RFfront-end transceivers with comparable performances with those in III-V compound semiconductor technologies. In addition, the device models in silicon-based process are more accurate and stable compared with those used for the III-V devices. Therefore, the silicon-based integrated circuits are more advantageous for low cost and mass production. This thesis deals with various design approaches of the siliconbased RF transceivers for high-performance wireless communication and sensing applications. This thesis consists with six chapters, each of which deals independent topics as below:

Chapter 1: A brief introduction to the advantage of silicon based process technology to support both micro- and millimeter-wave designs is discussed. And then, several examples of emerging micro- and millimeter-wave applications in sensing and communications are demonstrated.

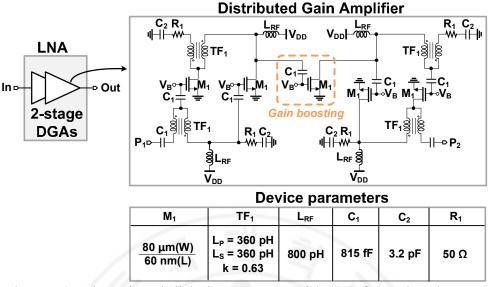

Chapter 2: An ultra-wideband low noise amplifier (LNA) is implemented in 65 nm CMOS. A compact inter-stage network utilizing one transformer and a de-Q-ing resistor for achievement of ultra-wide bandwidth is presented. The designed LNA achieves an input 1-dB compression point ( $IP_{1dB}$ ) of -21.43 dBm, maximum power gain of 18.21 dB over an ultra-wideband of 1 - 13 GHz, the measured minimum noise figure (NF) of 5.28 dB and. The realized LNA occupies 0.52 mm<sup>2</sup> of the active area excluding pads, and it consumes 14.92 mW from 1.2 V power supply.

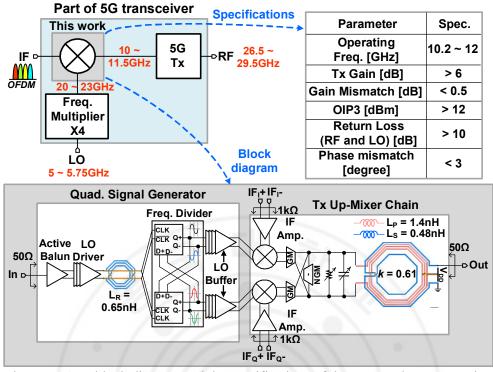

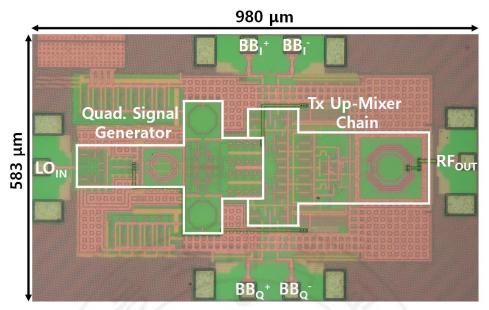

Chapter 3: A compact in-phase/quadrature (I/Q) up-conversion chain with high linearity is implemented in 65nm CMOS for an integrated transceiver for 5G mobile communications. The upconverter consists of  $10 \sim 11.5$  GHz up-conversion chains, a quadrature signal generator (QSG) based on the two coupled current-mode logic latches, and inverting amplifiers to provide the rail-to-rail local oscillator (LO) swing with a 25% duty cycle for I/Q mixers which has 46.9dB of image rejection ratio. In order to improve the output third-order intercept point (OIP3), a cross-coupled pair operating at weak inversion was used at the output of the upconverter. The upconverter achieved an OIP3 of 14.45dBm and a transmitter gain of 9.12dB. The realized I/Q upconverter with the QSG draws 48.7mW under a 1V supply, and chip area is only 0.57mm<sup>2</sup> including pads.

Chapter 4: An integrated 2–18 GHz four-channel compressed sensing receiver (CSRX), which performs a 128.5 × sub-Nyquist acquisition with 36-Gb/s pseudorandom bit sequence (PRBS) generators is implemented in 0.13-µm BiCMOS. The integrated four-channel CSRX includes broadband receiver chains, each of which includes a distributed RF buffer that operates as an active balun at 2–18 GHz, followed by a double-balanced passive mixer for high local-oscillator (LO)-tointermediate frequency (IF) isolation at the IF band, and a 700-MHz variable gain amplifier. In order to perform the compressed sensing by mixing the PRBS signal as the random modulator, four independent 36-Gb/s PRBS generators are integrated. So as to sufficiently deliver the generated wideband PRBS signal to the mixer, a shunt-shunt feedback amplifier is used by the LO driver to compensate for the highfrequency loss of the PRBS LO tones during the LO generation stage. The chip draws 195 mA per channel with a 2.5-V supply.

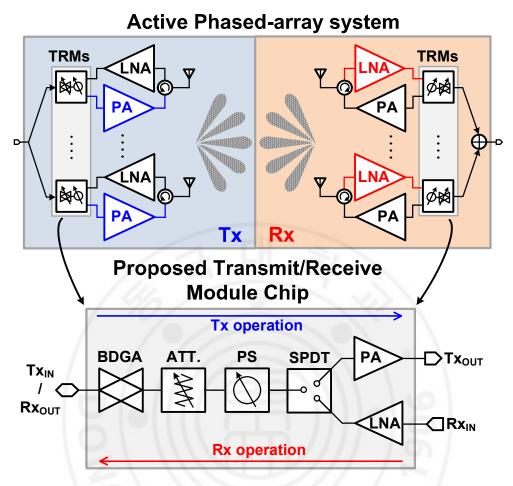

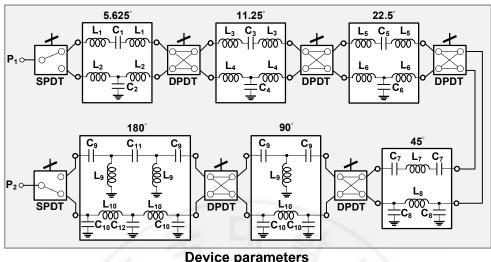

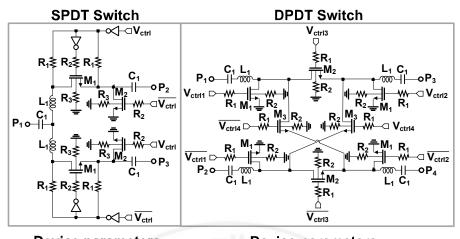

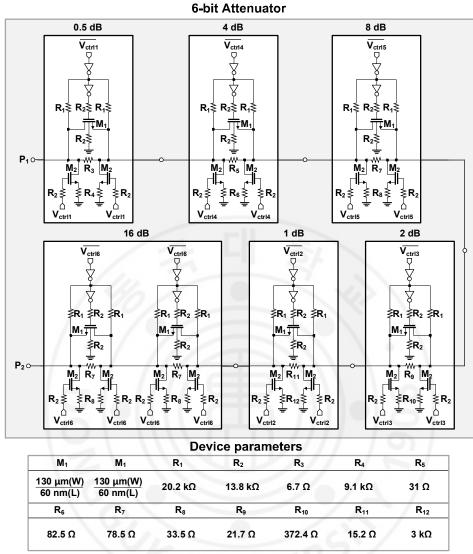

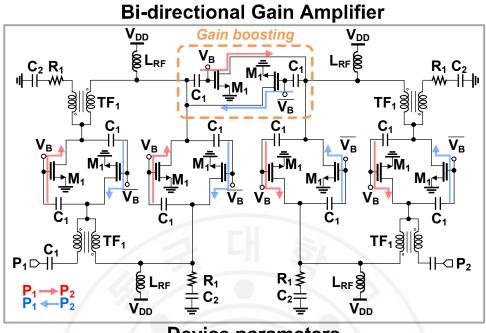

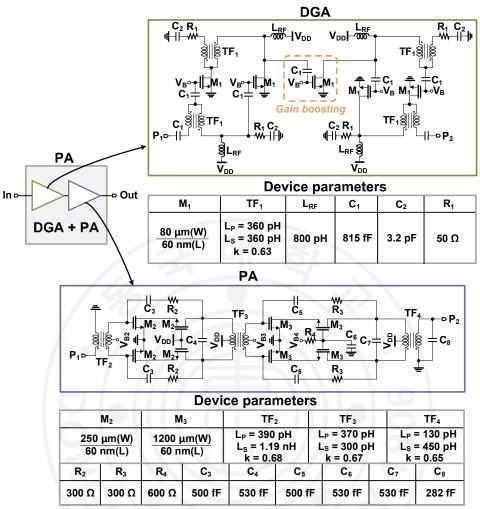

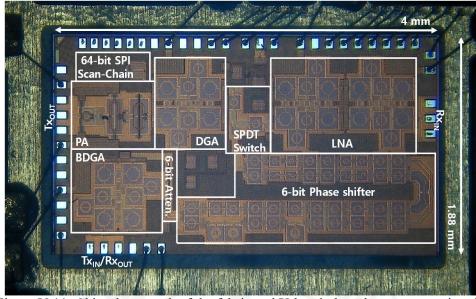

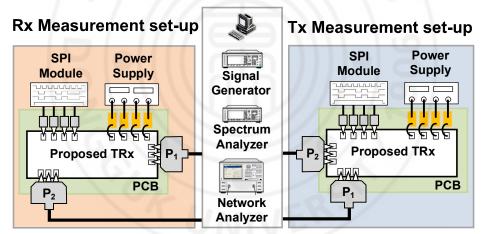

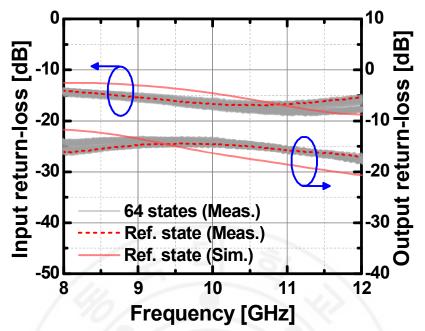

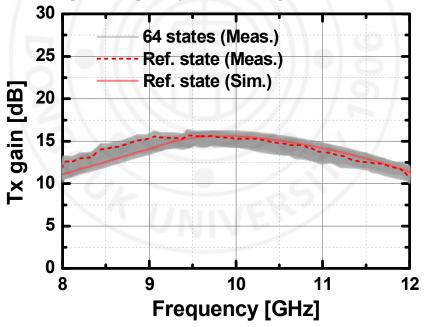

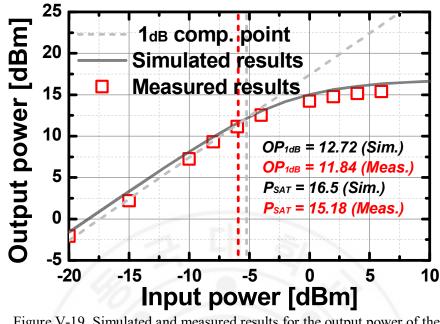

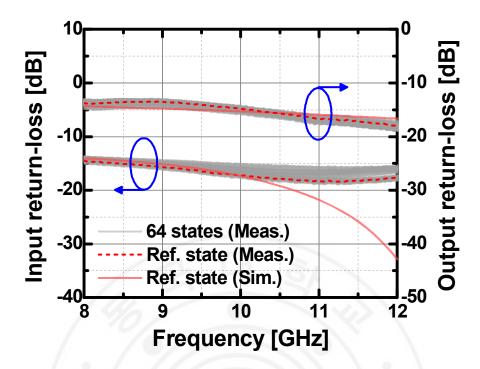

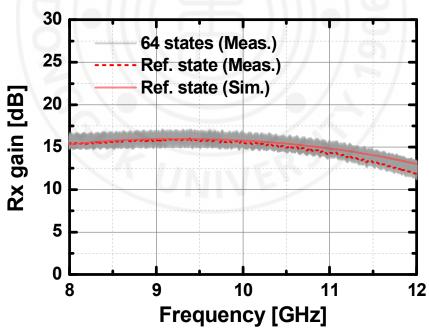

Chapter 5: a phased-array transceiver chip operating in full X-band (8-12 GHz) is realized in 65-nm CMOS technology. The implemented transceiver for the transmit/receive module (TRM) includes a single pole double throw (SPDT) switch connected to the internal power amplifier (PA) and the low-noise amplifier (LNA) to serve as a duplexer, a 6-bit passive phase shifter, a 6-bit attenuator, and a bi-directional gain amplifier (BDGA). For digital TRM control, a 64-bit SPI scan-chain is integrated. At the output 1-dB compression point ( $OP_{1dB}$ ) of 11.84 dBm, the

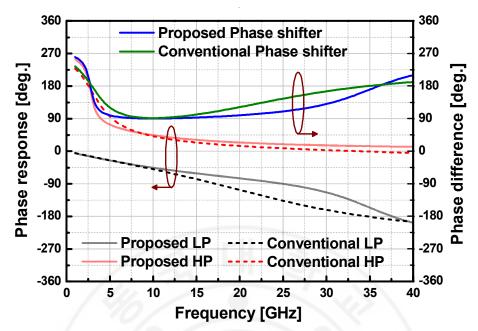

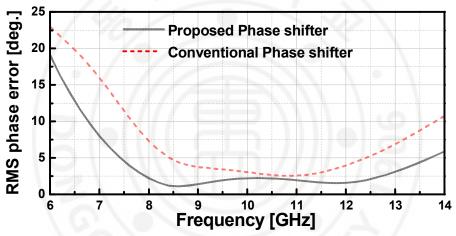

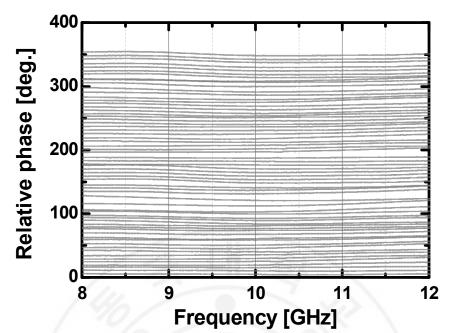

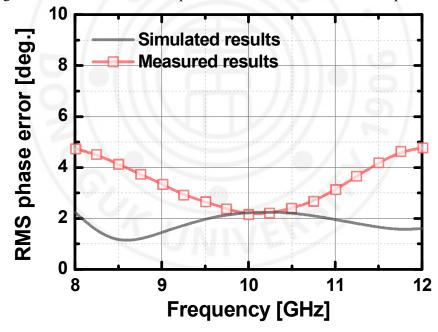

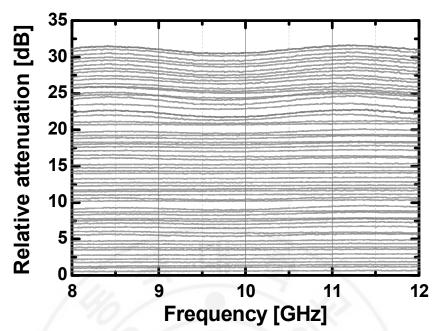

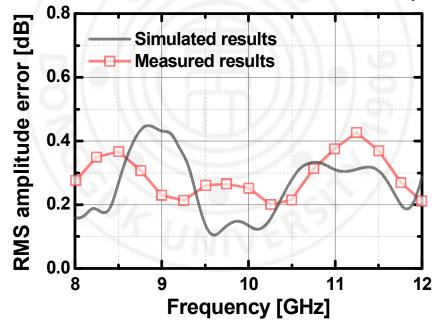

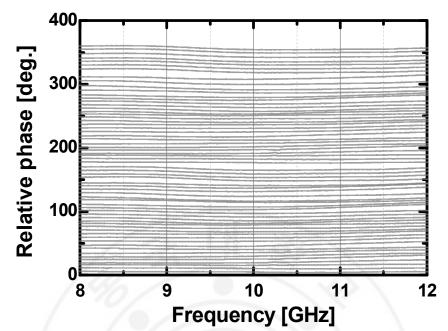

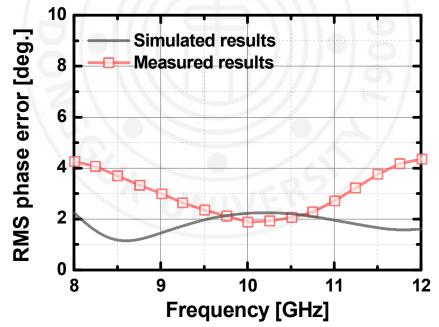

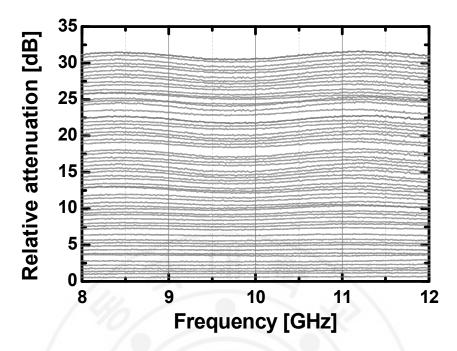

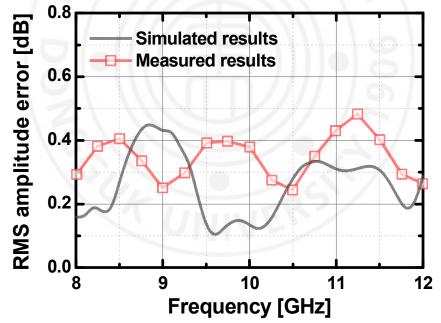

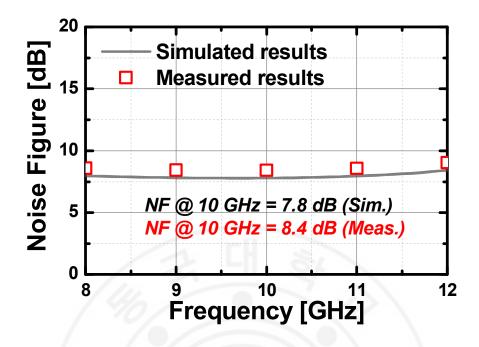

transmitter reaches power gain of more than of 15 dB. In order to achieve a wideband operation of the passive phase shifter, two different resonant frequencies for the phase leading and lagging networks are assigned, and are aligned the slopes of their phase responses to have the desired phase shifts at the center frequency. The RMS amplitude error is less than 0.45 dB, and the RMS phase error is less than 5° for all attenuation and phase states between 8-12 GHz while dissipating 216 mW dc power from a 1 V power supply. The receiver achieves noise figure (NF) of less than 8.4 dB and greater than 15 dB of power gain for the entire X-band. The RMS amplitude error and the RMS phase error are less than 0.45 dB and 5°, respectively, for all control states between 8-12 GHz. The receiver draws 110 mW with a 1 V power supply. The chip area of transceiver is  $4 \times 1.88$  mm<sup>2</sup>.

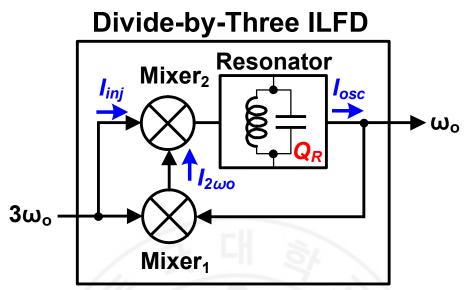

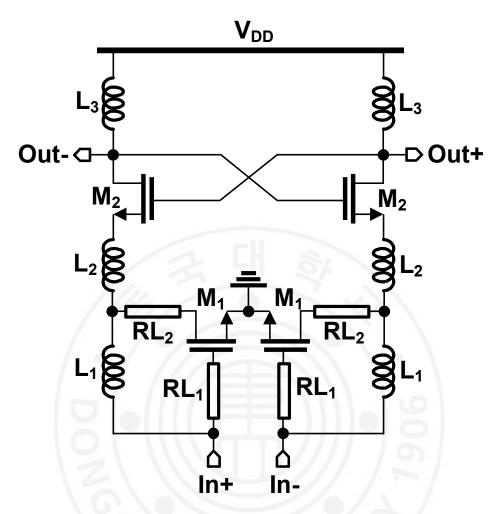

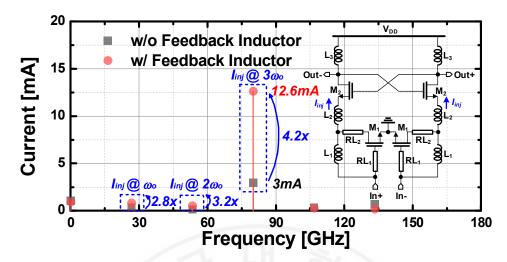

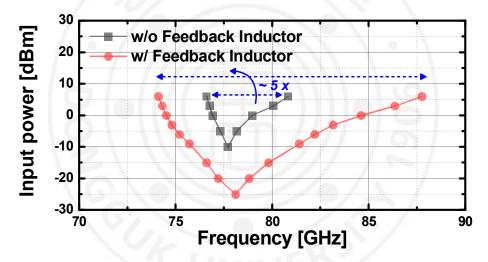

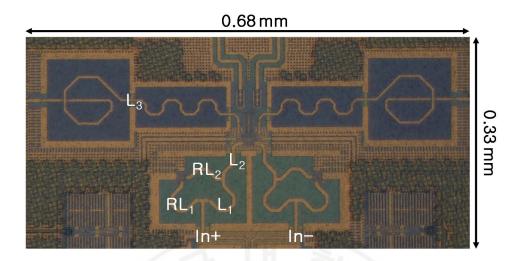

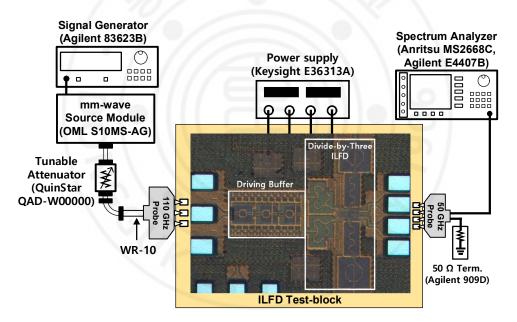

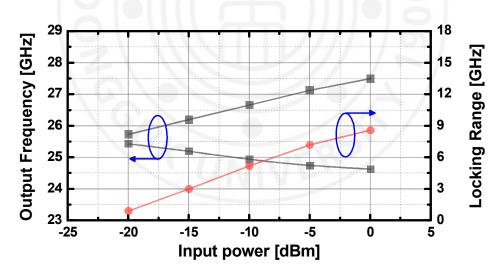

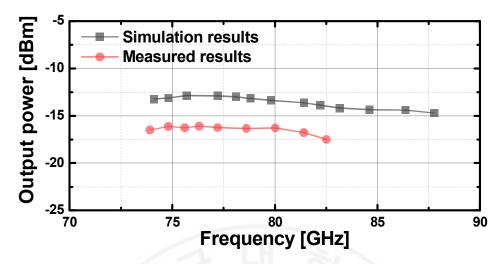

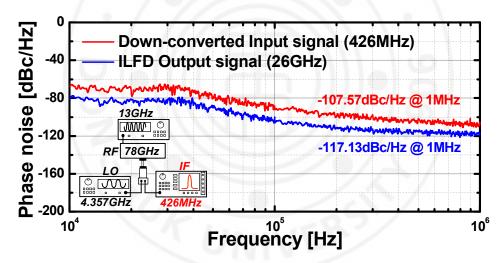

Chapter 6: A compact W-band divide-by-three injection locked frequency divider (ILFD) is realized in 65-nm CMOS technology. In order to provide a wide locking range, inductive feedback is used to boost the injection current. Under the suggested method, the ILFD's the locking range can be wider than 10% without additional power dissipation and any varactor which is more than three times the locking range compared with the reference ILFD without boosting of the current injection. With the W-band input signal power of 0dBm, the measured locking range of the proposed ILFD was from 73.9GHz to 82.5GHz. At the input frequency of 78GHz, the measured phase noise at 1MHz was -117.13dBc/Hz. The realized ILFD with the inductive feedback draws 7.88mW under a 1V supply. The core size of the ILFD is 0.22mm<sup>2</sup>.

### 국문초록

무선통신 및 센싱기술의 급격한 발달로 인해 단일 칩으로 기존의 시스템과 새로운 시스템 규격간의 호환이 가능하며 다양한 기능을 제공하는 송수신기 설계가 요구되고 있다. 이러한 최신 통신 및 센싱용 송수신기 설계는 충분한 RF 성능을 보장해야 할 뿐만 아니라 광대역 동작, 고선형, 소형화, 저전력소비, 저비용등 까다로운 요구사항을 만족해야 하는 과제를 지니고 있다. 최근, 실리콘 (CMOS 및 SiGe) 공정기술의 발달로 인해 III-V 족 화합물 반도체를 기반으로 하는 고성능 RF-front-end 의 성능에 준하는 시스템 반도체 회로설계가 가능하며, 핵심 반도체 소자 모델이 정확하고 공정의 안정성 또한 높아 저비용, 양산성 등에 유리하다. 본 연구는 소형화 및 저전력을 위한 실리콘

1 장 : 마이크로파 및 밀리미터파 설계가 적용되는 실리콘 기반 프로세스 기술의 장점에 대한 간략한 소개가 주어진다. 또한, 마이크로 및 밀리미터 파 대역의 센서 및 무선통신과 관련된 몇가지 일례를 간략히 설명한다.

2 장: 65nm CMOS 공정을 이용하여 초광대역 저잡음 증폭기를 구현하였다. 초광대역 대역폭을 달성하기 위해 하나의 transformer 와 De-Q-ing 저항으로 구성된 inter-stage network 를 설계하였다. 설계된 LNA 는 -21.43dBm 의 입력 1dB 압축 포인트 (IP<sub>1dB</sub>), 1-13GHz 의 초 광대역에서 18.21dB 의 최대 전력 이득,

iv

5.28dB의 측정된 최소 잡음 지수 (NF)를 달성하였다. 구현된 LNA는 패드를 제외한 0.52mm<sup>2</sup>의 칩면적을 차지하며 1.2V 전원에서 14.92mW 를 소비한다.

3 장 : 5G 이동통신용 송신기를 위해 높은 선형성을 갖춘 소형 I/Q (in-phase / quadrature) Up-conversion chain 이 65nm CMOS 공정으로 구현되었다. Upconverter 는 10 ~ 11.5GHz up-conversion chain 과 rail-to-rail LO 스윙을 제공하는 2 개의 전류 모드 로직(CML) 래치를 기반으로하는 QSG (Quadrature Signal Generator) 및 inverting 증폭기로 구성되었다. Image-rejection ratio 가 46.9dB 인 I / Q mixer 의 출력 3 차 인터셉트 포인트 (OIP3)를 개선하기 위해, weak-inversion 에서 동작하는 cross-coupled pair 가 upconverter 의 출력단에 사용되었다. 구현된 upconverter 는 14.45dBm 의 OIP3 와 9.12dB 의 송신 이득을 달성하였다. QSG 를 포함한 I/ Q upconverter 는 1V 전원에서 48.7mW 를 소비하며 칩 면적은 패드를 포함하여 0.57mm<sup>2</sup>이다.

4장: 36Gb / s PRBS (pseudo-random bit sequence) 발생기로 128.5 × 서브 나이퀴스트 수집을 수행하는 통합 2-18GHz 4 채널 압축 센싱 수신기 (CSRX)가 0.13µm BiCMOS 로 구현되었다. 통합된 4 채널 CSRX 에는 광대역 수신기 체인이 포함되어 있으며, 각각에는 2~18GHz 에서 active balun 으로 동작하는 분산형 RF 버퍼가 포함되어 있고, 높은 LO-to-IF 격리도를 위한 double-balanced passive mixer, 700MHz 의 대역폭을 갖는 IF 가변 이득 증폭기로 구성되었다. PRBS 신호를 랜덤 변조기로 사용하여 압축 센싱을 수행하기 위해, 4 개의 독립적인 36Gb/s PRBS 발생기가 설계되었다. 생성된 광대역 PRBS 신호를 mixer 에 충분히 전달하기 위해 LO driver 가 shunt-shunt feedback 증폭기로 구현되었으며, LO 생성 단계에서 PRBS LO 톤의 고주파 손실을 보상한다. 구현된 압축 센싱 수신기칩은 2.5V 전원으로 채널당 195mA 를 소비한다.

5장: 전체 X-대역 (8-12GHz)에서 작동하는 위상 배열 송수신기 칩이 65nm CMOS 공정으로 구현되었다. 송수신 모듈 (TRM)을 위해 구현된 송수신기는 전력 증폭기 (PA) 및 저잡음 증폭기 (LNA)에 연결된 duplexer 역할을 수행하는 SPDT (Single Pole Double Throw) 스위치, 6-bit 위상 변환기, 6-bit 감쇠기 및 양방향 이득 증폭기 (BDGA)를 포함한다. 디지털로 TRM 기능을 제어하기 위해 64-bit SPI 스캔 체인이 통합되어 있다. 위상 변환기의 광대역 동작을 달성하기 위해, 진상 (Leading) 및 지상 (Lagging) 네트워크에 대한 2 개의 상이한 공진 주파수가 할당되고, 중심 주파수에서 원하는 위상 시프트를 갖도록 위상 응답의 기울기를 보정하였다. 송신기는 1V 전원에서 216mW를 소비하며, 11.84dBm 의 출력 1dB 압축 지점 (OP1dB)에서 15dB 이상의 전력 이득을 갖는다. 또한, 8-12GHz 사이의 모든 감쇠 및 위상 상태에 대해 0.45dB 미만의 RMS 진폭 오류, 5° 미만의 RMS 위상 오류를 달성하였다. 수신기는 1V 전원으로 110mW 를 소비하며, 8.4dB 미만의 잡음 지수 및 15dB 이상의 전력 이득을 갖는다. 또한, 8-12GHz 사이의 모든 감쇠 및 위상 상태에 대해 RMS 진폭 오류 및 RMS 위상 오류는 각각 0.45dB 및 5 ° 미만이다. 송수신기의 칩 면적은 4 × 1.88 mm<sup>2</sup>이다.

vi

6 장 : W-대역 injection-locked 기반의 3 분주 주파수 분배기가 65nm CMOS 공정으로 구현되었다. 주파수 분배기의 locking range 를 wide 하게 구현하기 위해 주입 전류를 높이기 위한 inductive feedback 을 사용하였다. 제안된 방법 하에서 주파수 분배기의 locking range 는 추가적인 전력 손실 및 주파수 변경을 위한 varactor 없이 기존 주파수 분배기에 비해 3 배 이상 향상되었다. W-대역 입력 신호 전력이 0dBm 인 경우, 제안된 주파수 분배기의 측정된 locking range 는 73.9GHz 에서 82.5GHz 이다. 78GHz 의 입력 주파수에서 측정된 위상 노이즈는 1MHz offset 에서 -117.13dBc / Hz 이다. Inductive feedback 을 사용한 주파수 분배기의 코어 크기는 0.22mm<sup>2</sup> 이며 1V 전원에서 7.88mW를 소비한다.

# **TABLE OF CONTENTS**

| ABSTRACT                                                             | .i |

|----------------------------------------------------------------------|----|

| 국문초록                                                                 | iv |

| LIST OF FIGURES                                                      | x  |

| LIST OF TABLES                                                       | v  |

| I. Introduction                                                      | 1  |

| 1.1. Motivation and Background                                       |    |

| 1.2. Applications                                                    |    |

| 1.2.1. 5G Wireless communication                                     |    |

| 1.2.2. Compressed Sensing                                            |    |

| 1.2.3. Phased-array system                                           |    |

| 1.2.4. FMCW radar 1                                                  |    |

| 1.3. Thesis Organization1                                            | 2  |

| II. 1-13 GHz CMOS low-noise amplifier using compact transformer-base | ed |

| inter-stage networks1                                                |    |

| 2.1. Introduction 1                                                  |    |

| 2.2. Transformer-based UWB LNA 1                                     |    |

| 2.3. Measurement results 1                                           | 8  |

| III. Compact I/Q Up-Conversion Chain for a 5G Wireless Transmitter 2 | 22 |

| 3.1. Introduction                                                    | 22 |

| 3.2. Design of the I/Q Upconverter                                   | 23 |

| 3.3. Measurement results                                             | 27 |

| IV. 2–18 GHz Compressed Sensing Receiver with Broadband LO Chain3    | 62 |

| 4.1. Introduction                                                    | 2  |

| 4.2. The compressed sensing receiver design                          | 3  |

| 4.3.                                       | Measurement results                                                                                               |

|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| V. Fu                                      | ll X-band phased-array transmit/receive module chip43                                                             |

| 5.1.                                       | Introduction                                                                                                      |

| 5.2.                                       | X-band transceiver design                                                                                         |

| 5.2.1.                                     | 6-bit broadband passive phase shifter46                                                                           |

| 5.2.2.                                     | 6-bit step attenuator                                                                                             |

| 5.2.3.                                     | 1                                                                                                                 |

| 5.2.4.                                     |                                                                                                                   |

| 5.3.                                       | Measurement results                                                                                               |

|                                            |                                                                                                                   |

| VI. V                                      | V-Band Divide-by-Three Injection-Locked Frequency Divider With                                                    |

|                                            | V-Band Divide-by-Three Injection-Locked Frequency Divider With<br>n Current Boosting Utilizing Inductive Feedback |

|                                            |                                                                                                                   |

| Injectio                                   | n Current Boosting Utilizing Inductive Feedback                                                                   |

| <b>Injectio</b><br>6.1.<br>6.2.<br>6.3.    | n Current Boosting Utilizing Inductive Feedback                                                                   |

| <b>Injectio</b><br>6.1.<br>6.2.<br>6.3.    | n Current Boosting Utilizing Inductive Feedback                                                                   |

| <b>Injectio</b><br>6.1.<br>6.2.<br>6.3.    | n Current Boosting Utilizing Inductive Feedback                                                                   |

| Injectio<br>6.1.<br>6.2.<br>6.3.<br>VII. C | n Current Boosting Utilizing Inductive Feedback                                                                   |

## **LIST OF FIGURES**

| Figure I-1. Friis transmission equation [1]. $\lambda$ = Wave-length(m), $r$ = Distance (m),     |

|--------------------------------------------------------------------------------------------------|

| $P_T$ = Transmitted power (W), $G_T$ = Antenna gain for transmitter, $P_R$ = Received            |

| power (W), $G_R$ = Antenna gain for receiver                                                     |

| Figure I-2. Signal attenuation at sea level <i>versus</i> frequency2                             |

| Figure I-3. The generic system overview of a point-to-point radio2                               |

| Figure I-4. Data-rate versus process node and year [5]3                                          |

| Figure I-5. Maturation of $f_T$ in CMOS technology [6]4                                          |

| Figure I-6. Main process features of SiGe BiCMOS technology industrial                           |

| manufacturers [7]4                                                                               |

| Figure I-7. The current wireless standards spectrum allocation in North America5                 |

| Figure I-8. Block diagram of the broadband measurement system with Nyquist                       |

| sampling used for broadband signal measurement                                                   |

| Figure I-9. The spectrum slices from $x(t)$ are overlayed in the spectrum of the output          |

| sequences y[n]7                                                                                  |

| Figure I-10. Examples for multiple antenna system                                                |

| Figure I-11. A generic phased-array architecture9                                                |

| Figure I-12. Chirp Signal in the amplitude and frequency domains depending on time.              |

|                                                                                                  |

| Figure I-13. The workflow diagram for the FMCW radar                                             |

| Figure II-1. Schematic diagram of the proposed wideband LNA[30]15                                |

| Figure II-2. The small-signal equivalent circuit models for a conventional cascaded              |

| CS amplifier with a $\pi$ -type inductor peaking technique [31] and the proposed inter-          |

| stage network based on a single transformer                                                      |

| Figure II-3. Chip photograph of the LNA (Size : $0.43 \times 1.20 \text{ mm}^2$ including pads). |

|                                                                                                  |

| Figure II-4. Measured and simulated results of S-parameters for the LNA                          |

| Figure II-5. Measured and simulated results of P1dB for the LNA at 6 GHz 19                      |

| Figure II-6. Measured and simulated results of NF for the LNA19                                  |

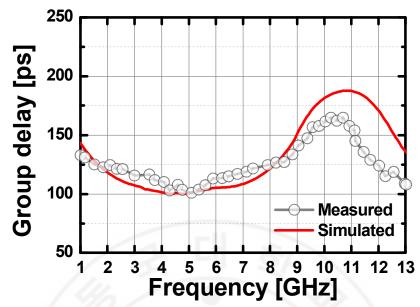

| Figure II-7. Measured and simulated results of group delay for the LNA20                         |

| Figure III-1. A block diagram and the specifications of the proposed up-conversio        |

|------------------------------------------------------------------------------------------|

| mixer for a 5G wireless transmitter [37]. The mixer consists of a quadrature signa       |

| generator and a Tx up-conversion chain [42]                                              |

| Figure III-2. Schematics of the (a) active balun, (b) unit-cells for the LO driver an    |

| buffer, (c) CML latch, (d) IF amplifier, and (e) double-balanced passive mixer2          |

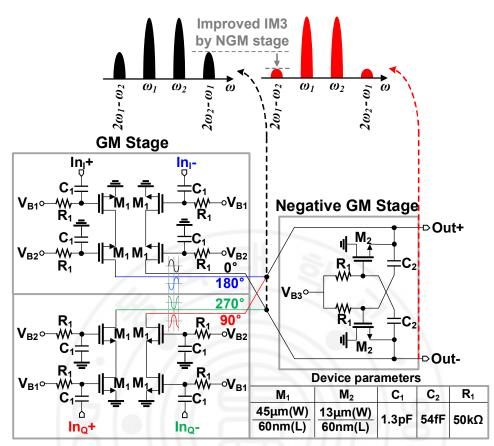

| Figure III-3. Schematic of the GM and NGM stages. It is noteworthy that the IM3 c        |

| the up-converted signal can be improved through the NGM stage2                           |

| Figure III-4. A photograph of the chip with the proposed up-conversion mixer with        |

| the QSG (chip size: 0.58 x 0.98mm <sup>2</sup> )2                                        |

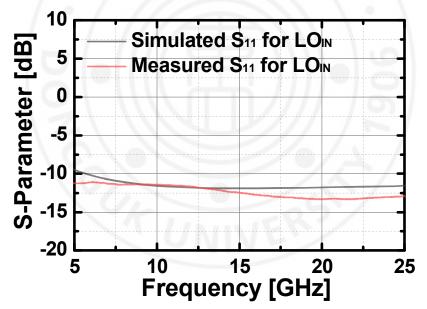

| Figure III-5. Measured and simulated S <sub>11</sub> for LO <sub>IN</sub>                |

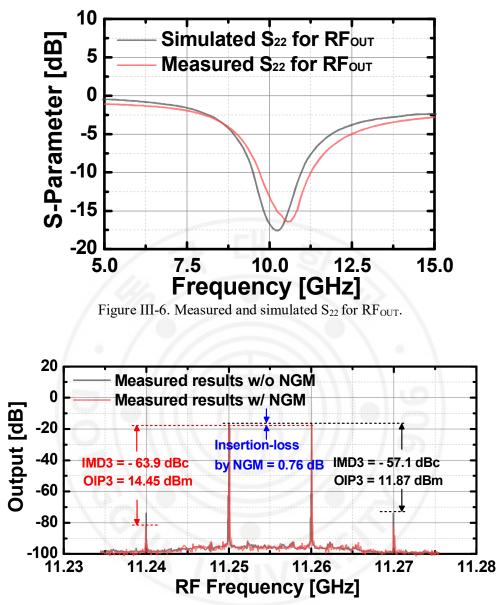

| Figure III-6. Measured and simulated S22 for RFOUT                                       |

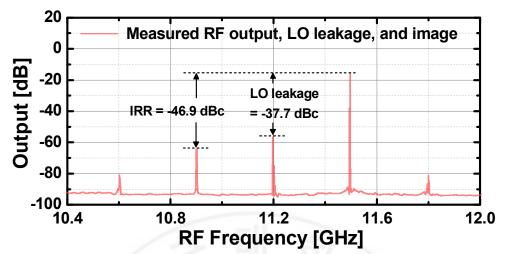

| Figure III-7. Measured up-converted RF output results with and without the NGM           |

| stage                                                                                    |

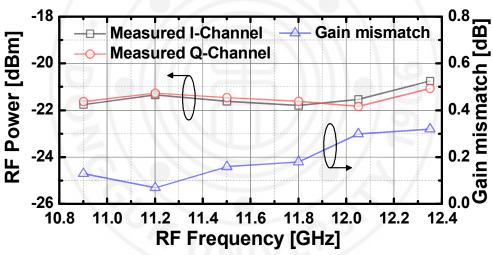

| Figure III-8. Measured RF output, LO leakage, and image with a single-tone input         |

| signal2                                                                                  |

| Figure III-9. Measured up-converted RF output results for the I/Q channels with less     |

| than 0.2dB of gain mismatch                                                              |

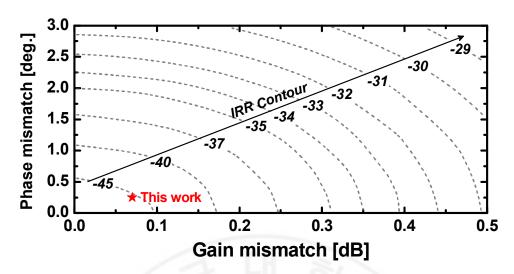

| Figure III-10. Phase mismatch based on the measured gain mismatch and IRI                |

| contour. The phase mismatch was expected to be lower than 0.5 degrees                    |

| Figure III-11. Measured and simulated results of gain and RF power for the               |

| implemented upconverter depending on IF power with $f_{\rm IF}$ = 300Mz and $f_{\rm LO}$ |

| 22.4GHz                                                                                  |

| Figure IV-1. A block diagram of the integrated 4-channel compressed sensing              |

| receiver in a 0.13-µm BiCMOS [54]                                                        |

| Figure IV-2. Schematics of (a) the distributed RF buffer and (b) the variable gai        |

| amplifier [54]                                                                           |

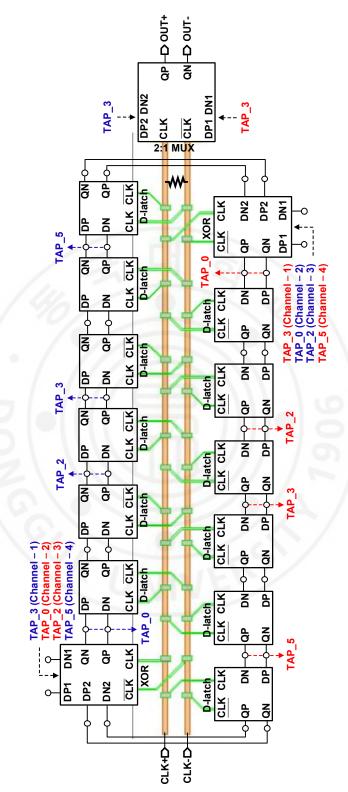

| Figure IV-3. Block diagram of PRBS generator                                             |

| Figure IV-4. (a) A block diagram and the frequency response of the band-equalize         |

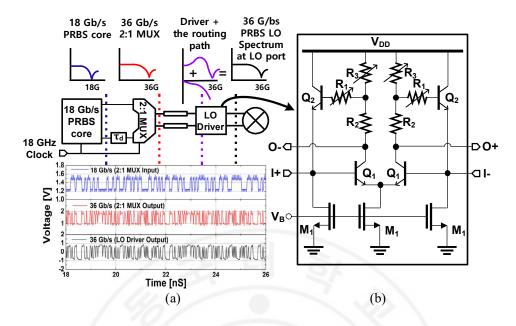

| LO generator and simulated PRBS pattern and (b) a schematic of the LO driver 3           |

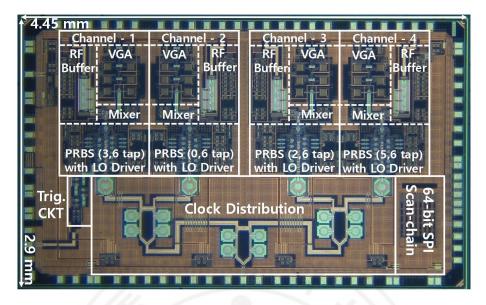

| Figure IV-5. A microphotograph of the implemented 4-channel CSRX chip (chi               |

| size = $2.9 \times 4.45 \text{ mm}^2$ )                                                  |

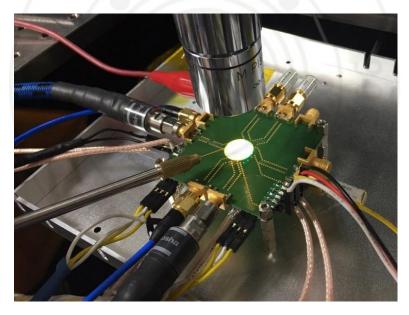

| Figure IV-6. The PCB of the packaged CSRX chip for the measurement                       |

| Figure IV-7. Measured and simulated $S_{11}$ results for the CLK and RF inputs in the           |

|-------------------------------------------------------------------------------------------------|

| CSRX                                                                                            |

| Figure IV-8. Measured LO-to-IF leakage at 18 GHz CLK input                                      |

| Figure IV-9. Measured IF output at 40 MHz, 240 MHz, and 320 MHz with a single                   |

| tone input at $f_{RF} = 2$ GHz for four independent CSRX channels                               |

| Figure IV-10. Spectra of the 18 GHz RF input signal (FM with a pulse signal) 39                 |

| Figure IV-11. One of the sensed repetitive IF signal of the FM input at 18 GHz with             |

| a pulse signal in the CSRX                                                                      |

| Figure IV-12 Spectra of the 18 GHz RF input signal (FM with a ramp signal)40                    |

| Figure IV-13. One of the sensed repetitive IF signal of the FM input at 18 GHz with             |

| a ramp signal in the CSRX                                                                       |

| Figure V-1. Block diagrams of the active phased-array system and proposed                       |

| transceiver configuration                                                                       |

| Figure V-2. Schematic and all device parameters of the proposed X-band 6-bit                    |

| passive phase shifter using HP/BP/LP networks                                                   |

| Figure V-3. The demonstration of bandwidth improvement of the proposed method.                  |

|                                                                                                 |

| Figure V-4. The simulated relative phase shift levels in all phase states                       |

| Figure V-5. The simulated RMS phase error of the proposed method and the                        |

| conventional method                                                                             |

| Figure V-6. Schematic [72] and all device parameters of the SPDT (left) and DPDT                |

|                                                                                                 |

| (right) switches                                                                                |

| (right) switches                                                                                |

|                                                                                                 |

| Figure V-7. Schematic and all device parameters of the designed X-band 6-bit step               |

| Figure V-7. Schematic and all device parameters of the designed X-band 6-bit step attenuator    |

| Figure V-7. Schematic and all device parameters of the designed X-band 6-bit step<br>attenuator |

| Figure V-7. Schematic and all device parameters of the designed X-band 6-bit step<br>attenuator |

| Figure V-7. Schematic and all device parameters of the designed X-band 6-bit step<br>attenuator |

| Figure V-7. Schematic and all device parameters of the designed X-band 6-bit step<br>attenuator |

| Figure V-7. Schematic and all device parameters of the designed X-band 6-bit step<br>attenuator |

| Figure V-13. Simulated and measured results for the $S_{11}$ and $S_{22}$ of the transceiver in |

|-------------------------------------------------------------------------------------------------|

| Tx operation depending on 64 different phase-shift states                                       |

| Figure V-14. Simulated and measured results for the Tx gain of the transceiver in Tx            |

| operation depending on 64 different phase-shift states                                          |

| Figure V-15. Measured relative phase shift of the transceiver in Tx operation64                 |

| Figure V-16. Simulated and measured results for the RMS phase error of the                      |

| transceiver in Tx operation                                                                     |

| Figure V-17. Measured relative attenuation level of the transceiver in Tx operation.            |

|                                                                                                 |

| Figure V-18. Simulated and measured results for the RMS amplitude error of the                  |

| transceiver in Tx operation                                                                     |

| Figure V-19. Simulated and measured results for the output power of the transceiver             |

| in Tx operation at 10 GHz                                                                       |

| Figure V-20. Simulated and measured results for the $S_{11}$ and $S_{22}$ of the transceiver in |

| Rx operation depending on 64 different phase-shift states                                       |

| Figure V-21. Simulated and measured results for the Rx gain of the transceiver in Rx            |

| operation depending on 64 different phase-shift states                                          |

| Figure V-22. Measured relative phase shift of the transceiver in Rx operation68                 |

| Figure V-23. Simulated and measured results for the RMS phase error of the                      |

| transceiver in Rx operation                                                                     |

| Figure V-24. Measured relative attenuation level of the transceiver in Rx operation.            |

|                                                                                                 |

| Figure V-25. Simulated and measured results for the RMS amplitude error of the                  |

| transceiver in Rx operation                                                                     |

| Figure V-26. Simulated and measured NF of the transceiver in Rx operation 70                    |

| Figure VI-1. A block diagram of the function of divide-by-three injection locked                |

| frequency divider (ILFD)                                                                        |

| Figure VI-2. Schematic of the proposed ILFD with inductive feedback for Iinj                    |

| boosting [102]74                                                                                |

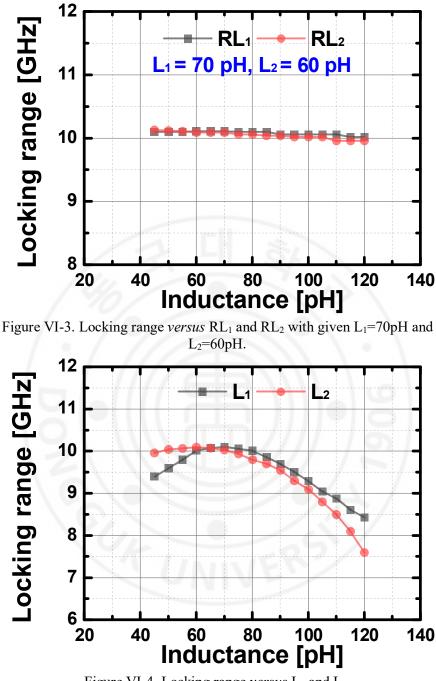

| Figure VI-3. Locking range versus $RL_1$ and $RL_2$ with given $L_1=70$ pH and $L_2=60$ pH.     |

|                                                                                                 |

| Figure VI-4. Locking range versus L <sub>1</sub> and L <sub>2</sub>                             |

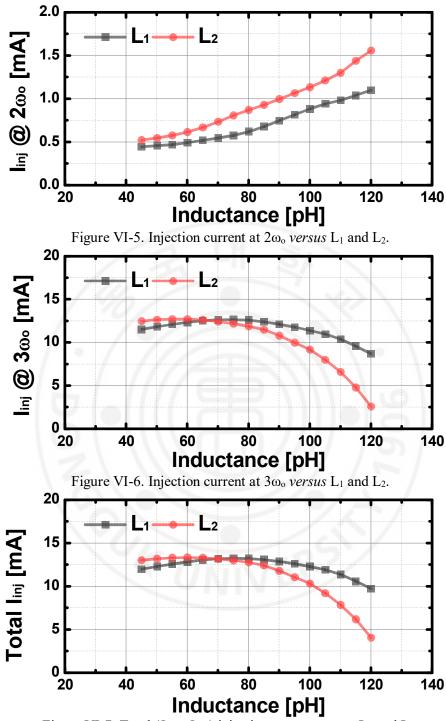

| Figure VI-5. Injection current at $2\omega_o$ versus $L_1$ and $L_2$                          |

|-----------------------------------------------------------------------------------------------|

| Figure VI-6. Injection current at $3\omega_o$ versus $L_1$ and $L_2$                          |

| Figure VI-7. Total ( $I_{2\omega o}+I_{3\omega o}$ ) injection current versus $L_1$ and $L_2$ |

| Figure VI-8. Simulated injection current with and without feedback inductor for the           |

| proposed ILFD77                                                                               |

| Figure VI-9. Simulated locking range with and without feedback inductor for the               |

| proposed ILFD77                                                                               |

| Figure VI-10. A microphotograph of the proposed ILFD chip with the inductive                  |

| feedback (core size: 0.68 x 0.33 mm <sup>2</sup> )                                            |

| Figure VI-11. Measurement set-up for the proposed ILFD test-block with driving                |

| buffer                                                                                        |

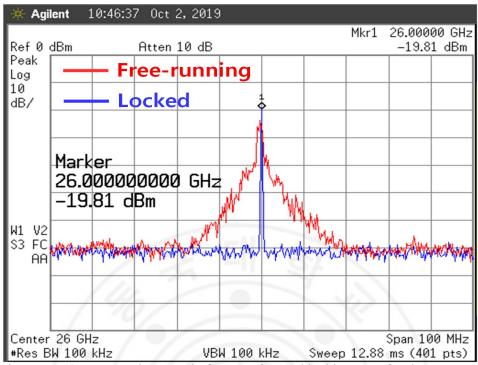

| Figure VI-12. Measured spectra in free-running and locking state for the proposed             |

| ILFD with input frequency of 78GHz79                                                          |

| Figure VI-13. Measured sensitivity curve and locking range for the proposed ILFD.             |

|                                                                                               |

| Figure VI-14. Simulated and measured output power for the proposed ILFD with                  |

| input power of 0dBm. The measured output power is considered the loss caused by               |

| probe-tip and cable                                                                           |

| Figure VI-15. Measured phase noise for the proposed ILFD in locking condition.                |

| The phase noise of the input frequency was measured using by harmonic mixer                   |

| (Agilent 11970W)                                                                              |

|                                                                                               |

|                                                                                               |

|                                                                                               |

# LIST OF TABLES

| Table II-1. Summary of the proposed LNA and comparison with previously           |

|----------------------------------------------------------------------------------|

| published CMOS LNAs                                                              |

| Table III-1. Comparison with previously reported up-conversion mixers            |

| Table IV-1. Comparison with previously reported state-of-art CSRXs in integrated |

| spectrum sensors                                                                 |

| Table V-1. Comparison with previously reported state-of-the-art X-band phased-   |

| array transceivers                                                               |

| Table VI-1. Comparison with previously reported mm-wave CMOS divide-by-three     |

| injection locked frequency dividers                                              |

### I. Introduction

### 1.1. Motivation and Background

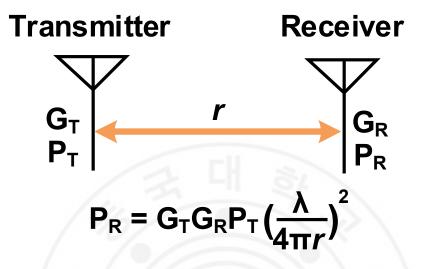

Figure I-1. Friis transmission equation [1].  $\lambda$  = Wave-length(m), r = Distance (m),

$P_T$  = Transmitted power (W),  $G_T$  = Antenna gain for transmitter,  $P_R$  = Received power (W),  $G_R$  = Antenna gain for receiver.

In the past decades, wireless communication and sensing systems have been made rapid progress with the steadily increasing the use of frequency bands for much faster and larger data transfers. Especially, the demand for extremely high-frequency (micro-wave and mm-wave) transceivers in the systems is exploding. Here, micro-wave and mm-wave spectrums classified as extremely high-frequency are defined as 1-30 GHz and 30-300 GHz, respectively. However, the system with high-frequency propagation cannot avoid high path-loss in a transmit/receive channel path. To be more specific, the Friis transmission equation [1] used to relate the received power ( $P_R$ ) and transmitted power ( $P_T$ ) in the channel should be considered to successfully implement the systems, as shown in Figure I-1.

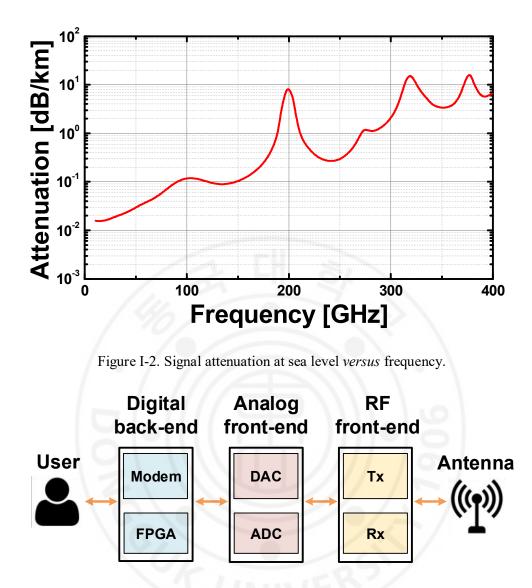

In addition, the absorb by rain, fog, and moisture for micro- and mm-waves in the air can reduce the data transmission distance resulting in signal attenuation. For example, the signal attenuation by Oxygen (O<sub>2</sub>) absorption is extremely high at 60

Figure I-3. The generic system overview of a point-to-point radio.

GHz as depicted in Figure I-2. Therefore, the frequency within the curve valleys in Figure I-2 should be carefully selected so as to minimize the attenuation. Additionally, a design of high-gain antenna can help with the boosted effective isotropic radiated power (EIRP) to improve the data transmission range in the systems.

Wireless products in micro-/mm-wave applications require demanding properties such as low cost, low power, high performance and large capacity. In order

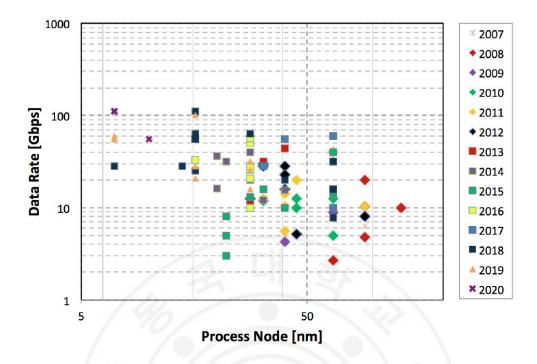

Figure I-4. Data-rate versus process node and year [5].

to implement the wireless communication and sensing systems, the RF-front-end is one of the key blocks in the systems as shown in Figure I-3. Historically, the systems in mm-wave applications have been dominated by III-V compound semiconductor technologies (mainly Gallium Arsenide (GaAs) and Indium Phosphide (InP)) [2-3]. However, passive elements such as inductor, capacitor, and transmission line for impedance matching and tuning are essential for the design of RF-front-end in the systems, and these elements occupy most of the chip area. Since the process cost of III-V compound semiconductor technology is quite expensive, there are limitations in implementing a fully integrated on-chip system. Therefore, the challenges are to build the RF transceiver front-end on a single chip, and to minimize the area and cost of the chip.

Recently, since the size of silicon-based transistors have steadily decreased based on Moore's law [4], improvements in integrated circuit (IC) technology with high data rate have also been made at the same time as shown in Figure I-4 [5]. With the reduced channel length, the RF characteristics of silicon-based processes (*i.e.*, SiGe BiCMOS and CMOS) such as the cut-off frequency ( $f_t$ ) and maximum

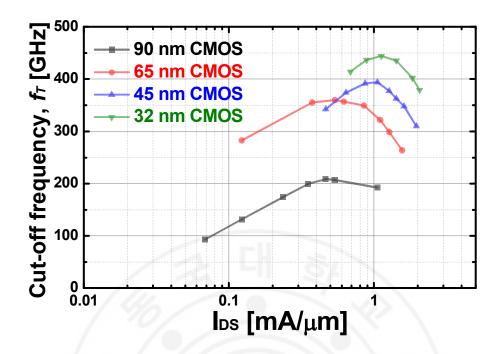

Figure I-5. Maturation of  $f_T$  in CMOS technology [6].

| Company <sup>1</sup>           | Free                     | scale                  | IBM                       |                        | Infineon                 |                                            | TowerJazz                                                |             | STMicroelectronics                |                                                       |                          |

|--------------------------------|--------------------------|------------------------|---------------------------|------------------------|--------------------------|--------------------------------------------|----------------------------------------------------------|-------------|-----------------------------------|-------------------------------------------------------|--------------------------|

| Name                           | HIP6MW                   | HiP6MW2                | BICMOS8HP BICMOS8XP       |                        | BICMOS9HP                | B7HF200                                    | B11HFC                                                   | SBC18H3     | SBC18H4                           | BICMOS9MW                                             | BICMOS055                |

| Status                         | Prod.                    | Dev                    | Prod.                     | Prod?                  | Dev.                     | Prod.                                      | Dev.                                                     | Prod.       | Dev.                              | Prod.                                                 | Dev.                     |

| CMOS node                      | 180nm                    |                        | 130nm                     |                        | 90nm                     | Bipolar-<br>only                           | 130nm                                                    | 180nm       | 180nm                             | 130nm                                                 | 55nm                     |

| Wafer Size                     | 200mm                    |                        |                           | 200mm                  |                          | 200mm                                      |                                                          | 200mm       |                                   | 200mm                                                 | 300mm                    |

| SiGe HBT<br>structure          | Self-aligned<br>SEG epi. |                        | Self-aligned<br>NSEG epi. |                        | Self-aligned<br>SEG epi. |                                            | Self-aligned<br>NSEG epi.                                |             | Self-aligned<br>SEG epi.          |                                                       |                          |

| SiGe HBT<br>ft / fMAX<br>(GHz) | 200 / 280                | 260 / 350              | 210 / 270                 | 260 / 320              | 300 / 350                | 190 / 250                                  | 240 / 380                                                | 240 / 270   | 275 / 350<br>(tbc)                | 220 / 280                                             | 320 / 370                |

| BEOL (w/o<br>Alu cap)          |                          |                        |                           | Al levels<br>+ 4.0 µm) | NA                       | 4 Cu<br>levels<br>(0.6/0.6/1.2)<br>2.5 μm) | 6 Cu levels<br>(0.29/0.32/0.3<br>/ 2/0.32/1.0/2.8<br>μm) | with at lea | Al levels<br>ast 1 thick<br>netal | 6 Cu levels<br>(0.26/0.35/0.3<br>5/0.9/3.0/3.0µ<br>m) |                          |

| TL<br>(µ-strip)                | 1.25<br>dB/mm<br>@ 77GHz | <1<br>dB/mm<br>@ 80GHz | 0.9 dl<br>@ 60            |                        | NA                       | NA                                         | NA                                                       | NA          | NA                                | 0.5<br>dB/mm<br>@ 60GHz                               | 0.65<br>dB/mm<br>@ 50GHz |

Figure I-6. Main process features of SiGe BiCMOS technology industrial manufacturers [7].

frequency of oscillation ( $f_{max}$ ) was significantly improved as illustrated in Figures I-5 and 6 [6-7]. As can be seen from the Figures, the Silicon-based RF transceiver front-end can be fully integrated with the analog front-end and digital back-end on a single chip.

#### **1.2.** Applications

The following sections will illustrate some of wireless communication and sensing applications in micro- and mm-wave bands.

### 1.2.1. 5G Wireless communication

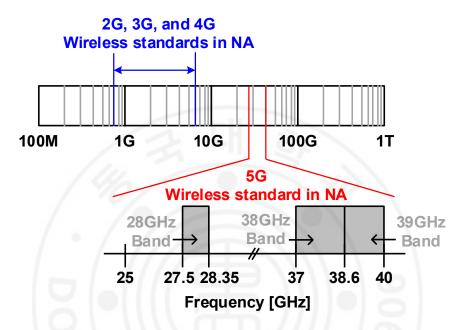

Figure I-7. The current wireless standards spectrum allocation in North America.

We are now living in a 5G era that supports massive MIMO (Multiple-Input-Multiple-Output) communication, Device-to-Device (D2D) communication, and Machine-to-Machine (M2M) communication [8-9]. Figure I-7 shows North America's current cellular wireless standard spectrum allocation for the International Telecommunications Union (ITU) radio bands scale. The limited bandwidth of the f spectrum below 6 GHz cannot meet the mobile traffic explosion in the current era. Therefore, for higher data rate and wider bandwidth, a spectrum is used in the mmwave band for the 5G standard [10-11]. This is made possible by the advance in semiconductor technology that can build silicon-based integrated circuits (ICs) and systems-on-chips (SoCs) in mm-wave band [12]. 5G is in place in the mm-wave frequency range, and the Federal Communications Commission (FCC) recently allocated a total of 3.85 GHz bandwidth for use in the 5G standard in the 28 GHz, 38 GHz and 39 GHz bands as shown in Figure I-7 [13].

#### 1.2.2. Compressed Sensing

Figure I-8. Block diagram of the broadband measurement system with Nyquist sampling used for broadband signal measurement.

Figure I-8 shows the general configuration of a broadband RF signal acquisition system based on the Nyquist sampling theory [14]. The broadband signal acquisition system consists of a front-end block that receives a wideband high-frequency signal through an antenna which generates an analog signal suitable for the input of the ADC by performing amplification, filtering. The output signal of the front-end is processed for real-time digital acquisition at a high-speed back-end block. The back-end block consists of a high-speed FPGA, an ultra-high speed ADC of several tens of Gb/s, a high-speed memory, a high-speed data transmission device, and a digital signal processing (DSP) with a high computation power for processing massive digital data sets.

Nowadays with the advancement of silicon technology, 20 Gb/s or even faster interleaved ADCs with have been reported as an integrated circuit (IC) [15]. However, to process broadband signals in real-time, a multiple-interleaved architecture consisting of high-speed ADCs has to be implemented as an expensive module which consumes tens of watts of power, and its size is also considerably bulky [16]. Therefore, it is challenging to implement a receiver that collects unidentified signals at micro-wave range with Nyquist theory, especially when we want to implement a miniaturized micro-wave receiver for real-time signal acquisition with relatively low power consumption.

Recently, a compressed sensing receiver that can perform a real-time signal reconstruction has been presented as an excellent alternative to avoid aforementioned

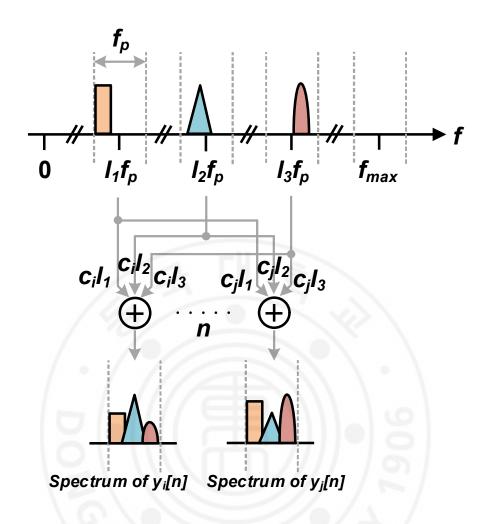

Figure I-9. The spectrum slices from x(t) are overlayed in the spectrum of the output sequences y[n].

issues. As depicted in Figure I-9, when the input signal is sparse, it has been shown that the signal reconstruction is possible even with sub-Nyquist sampling frequency by utilizing a random sensing matrix that meets the restricted isometry property (RIP) condition. This compressed sensing theory is being actively researched to speed up, optimize, and simplify signal processing systems in various fields such as wireless channel estimation in the wireless communication field, high-resolution radar signal surveillance for broadband signals, and medical image signal processing.

#### 1.2.3. Phased-array system

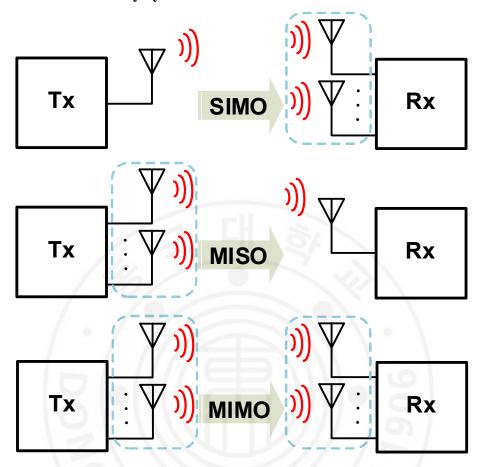

Figure I-10. Examples for multiple antenna system.

Multiple antenna system is capable of steering nulls and lobes of an antenna beam to reduce delay spread of the channel and to improve signal-to-noise ratio (SNR), by implementing beamforming. The system can be implemented on either the transmit side (multiple-input single-output: MISO), the receive side (signal-input multiple-output: SIMO), or both sides (multiple-input multiple-output: MIMO) [17] as shown in Figure I-10. Especially, the MIMO system utilizes antenna space diversity to create an independent channel path, and then, combines the received signal in an optimum way using space-time processing [18-20]. The implementation for the MIMO system based on the multiple antennas has intrigued industrial efforts and huge number of research in last decade.

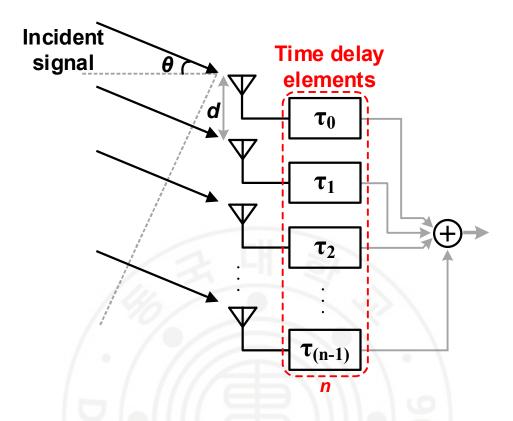

Figure I-11. A generic phased-array architecture.

Even though the multiple antenna system can be easily implemented to the base station for a wire-less mobile communication [21], the system is not suitable for mobile devices. This is because it requires the comparatively higher power according to small hardware sharing. And also, an antenna separation on the order of a magnitude, which can be higher than the wavelength, is needed to obtain a low channel correlation coefficient [22]. In order to solve these problem, the phased array system is introduced. A phased array receiver consists of independently separated signal paths, each of which is connected to separate antenna. Generally, incident signal from radiated transmitter arrives at spatially-separated antennas at different times as shown in Figure I-11. An ideal phased-array system with a time delay element such as phase shifter compensates the time delay, and combines the signals coherently to enhance the receiver sensitivity from the desired direction while rejecting receptions from other directions.

#### 1.2.4. FMCW radar

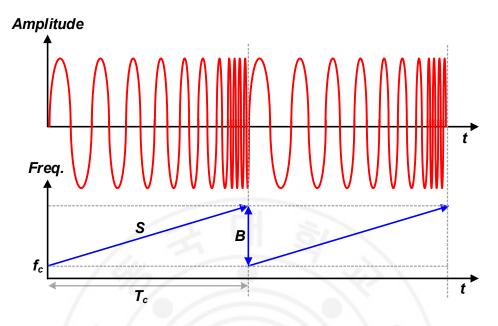

Figure I-12. Chirp Signal in the amplitude and frequency domains depending on time.

The main concept of frequency modulated continuous wave (FMCW) radar is a signal which is known as a chirp. The signal can be defined as a sinusoidal wave with a frequency value that increases linearly depending on time as shown in Figure I-12. The characteristic of the chirp signal with linear increase can create the sawtooth type frequency like the blue-colored line in Figure I-12. As can be seen from Figure I-12, we can define four important characteristics that demonstrate the chirp signal. First of all, the frequency of  $f_c$  is the initial frequency. Secondly, the frequency sweep bandwidth of B represents the frequency interval between the start and end. Thirdly, the chirp duration of  $T_c$  represents the allocated cycle time for the chirp. Finally, the chirp slope of S represents the rate of change of the chirp signal frequency per unit of time, and can be defined as below

$$S = \frac{B}{T_C} \tag{1-1}$$

\_

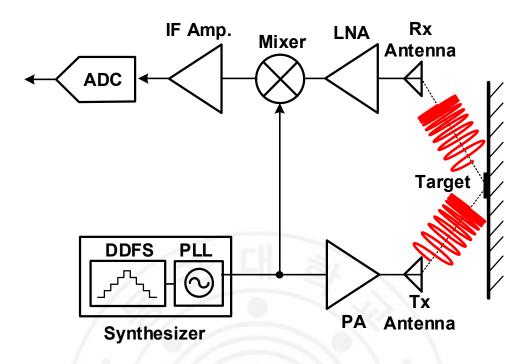

Figure I-13. The workflow diagram for the FMCW radar.

As shown in Figure I-13, the workflow diagram for the FMCW radar is presented as follows. Initially, an on-chip synthesizer (composed by DDFS and phase-locked loop) creates the chirp signal based on the different user-configurable chirp parameters. Once the chirp is amplified by a power amplifier and transmitted through Tx antenna, the Rx antenna detects the reflected and delayed chirp signal as compared with original chirp signal. The received signal is amplified by a low-noise amplifier (LNA), and then, is mixed with the original chirp signal to generate the beat frequency or IF signal. Finally, the down-converted IF signal can be amplified by an IF amplifier, and then, delivered to an ADC. The resulting serialized digital signal from the ADC can be ready to be transmitted to any other device.

#### **1.3.** Thesis Organization

In this study, the designs of RF transceiver front-end for silicon-based wireless communication and sensing applications in micro- and mm-wave bands with chip miniaturization and low power consumption are discussed.

In chapter 2, a compact wideband matching network utilizing a single transformer and a de-Q-ing resistor, where the negatively coupled transformer, is proposed so as to achieve considerable size reduction compared with the  $\pi$ -type inductor peaking (PIP) network.

In chapter 3, a compact I/Q upconverter as an IF up-mixer block with a bandwidth of 800MHz for a 5G wireless transceiver is presented. The upconverter with a QSG achieves high linearity by utilizing a cross-coupled pair operating at the weak inversion region to provide 3rd harmonic compensation from the GM stage for IM3 improvement. To generate I/Q signals with 25% of the duty cycle from the available  $2f_{LO}$  signal, we utilized a frequency divider based on current-mode logic (CML) latches for the compact implementation of the QSG.

In chapter 4, an ultra-fast CSRX with a  $128.5 \times$  sub-Nyquist acquisition for the spectrum monitoring in the range of 2–18 GHz is described. To achieve broadband operation, we implemented broadband LO chain with a shunt-shunt feedback amplifier with equalization capability. The implementation of microwave broadband compressed sensing is achieved based on the concept of the analog-to-information converter (AIC).

In chapter 5, a fully integrated TRM chip operating in full X-band (8 – 12 GHz) is implemented in 65-nm CMOS technology. Compared with the previous work, the proposed TRM chip is designed to cover the full X-band by designing a broadband phase shifter, and a high-performance power amplifier is designed in the Tx path to achieve output power higher than 11 dBm. The implemented transceiver achieves an RMS phase error of less than 5°, and an RMS attenuation error of less than 0.45 dB with linearity and noise performance comparable to the recently reported SiGe transceiver and III-V TRM MMICs, and with much lower power consumption.

In chapter 6, a W-band divide-by-three ILFD with an inductive feedback network is proposed to enhance the injection current without any frequency tuning component like a varactor or additional power consumption in achieving a wider locking range.

In chapter 7, the research of RF transceiver front-end designs for wireless communication and sensing applications concludes.

### II. 1-13 GHz CMOS low-noise amplifier using compact transformer-based inter-stage networks

#### 2.1. Introduction

Developing exploration on ultra-wideband (UWB) frameworks has expanded enthusiasm for broadband low-noise amplifier (LNA) design. A broadband LNA must have low noise figure (NF) and good input matching over a multi-GHz bandwidth (BW) with low power dissipation. The UWB LNA ought to be deliberately intended to give an adequately enormous amount of power gain with minimum noise added to the framework. In UWB framework, LNA is required to achieve a moderate passband gain with low group delay over the passband. In addition, it should provide the wideband impedance matching to 50  $\Omega$  at the input to minimize the signal reflection at interface between a receiving antenna or band-pass filter (BPF) and the LNA input.

A multiple-section bandpass filter with inductively generated common-emitter (CE) SiGe, or common-source (CS) CMOS LNA have been proposed in [23-24] so as to achieve wideband impedance matching. As compared with the CS-LNA, the common-gate (CG) LNA proposed in [25] can reduce power consumption and improve the linearity. However, the large number of inductors increased the NF and also consumes a significant amount of chip area. Using a common gate (CG) transistor for input matching is proposed in [26-28], but the additional CS stage consumes more power and degrades the linearity. In order to achieve the capacitor cross-coupled g<sub>m</sub>-boosting, a differential CG-LNA with stagger-compensated series-peaking technique is reported in [29]. However, the capacitor coupled g<sub>m</sub>-boosting has slightly better noise performance, but cause potential instability though it.

Figure II-1. Schematic diagram of the proposed wideband LNA[30].

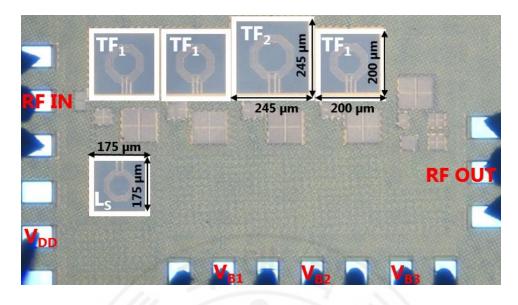

### 2.2. Transformer-based UWB LNA

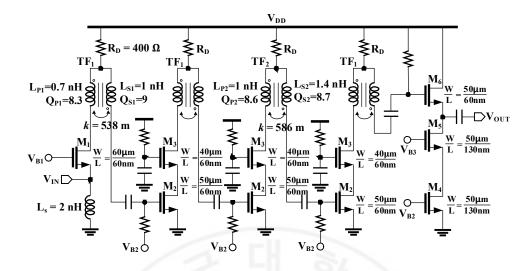

Figure II-1 shows a schematic diagram for the LNA. The designed LNA consists of five stages, each of inter-stage network is utilizing a de-Q-ing resistor and a single transformer for a wide bandwidth. The proposed compact transformer-based inter-stage network has comparable bandwidth enhancement ratio (BWER) as for the  $\pi$ -type inductor peaking (PIP) network with much smaller area consumption[30]. The designed 1-13GHz LNA is intended for an UWB radar in motion sensing and high precision-ranging applications.

A CG amplifier with a source inductor is used as the first stage to provide a wideband 50  $\Omega$  matching at the input. The source inductor is to provide the bias current and to increase the input bandwidth by resonating out the node capacitance at the center frequency while achieving a moderate NF and a good linearity. In order to achieve a wideband inter-stage network with compact area occupation, total five stages are cascaded, each of which utilizes drain and gate parasitic capacitances and a transformer with a series resistor.

After the CG stage, for a wideband output impedance matching, it has three consecutive cascode amplifiers followed by the source follower at the output stage. With a desired bandwidth of 1 - 13 GHz each transformer's self-resonance frequency

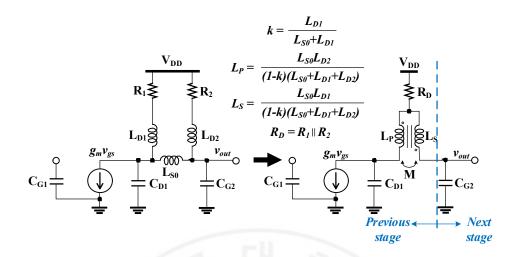

Figure II-2. The small-signal equivalent circuit models for a conventional cascaded CS amplifier with a  $\pi$ -type inductor peaking technique [31] and the proposed interstage network based on a single transformer.

should be higher than the highest operating frequency to ensure stable operation of the circuit.

In [31],  $\pi$ -type inductor peaking (PIP) approach is proposed to achieve BWER greater than 3. Although PIP can greatly increase the bandwidth of the cascaded amplifier, three separate inductors (L<sub>D1</sub>, L<sub>D2</sub>, and L<sub>s0</sub> in Figure II-2) and two resistors (R<sub>1</sub> and R<sub>2</sub> in Figure II-2) are required for each inter-stage of the cascaded amplifiers, rendering the multistage amplifier quite bulky. This massive PIP can be effectively approximated into a single compact transformer with a small resistor as shown in Figure II-2. The trans-impedance transfer-function  $Z_{TF}(s)$  for an inter-stage network based on a negatively coupled transformer is derived as follows:

$$Z_{TF}(s) = \frac{v_{out}}{-g_m v_{gs}} = -\frac{sM - R_D}{1 + sA_0 + s^2 A_1 + s^3 A_2 + s^4 A_3}$$

(2-1)

where

$$M = k \sqrt{L_{P}L_{S}}$$

$$A_{0} = R_{D}(C_{G2} + C_{D})$$

$$A_{1} = C_{D}L_{P} + C_{G2}L_{S}$$

$$A_{2} = C_{D}C_{G2}R_{D}(L_{P} + L_{P} + 2M)$$

$$A_{3} = C_{D}C_{G2}L_{P}L_{S}(1 - k^{2})$$

(2-2)

Through using the proposed inter-stage network based on transformer as a compact wideband matching network, BWER is comparable to PIP approach with far smaller occupancy area. The ultra-thick metal (UTM) with the thickness of 3  $\mu$ m is used to minimize the ohmic loss for the transformer windings. The designed TF<sub>1</sub> and TF<sub>2</sub> occupy an area of 200 x 200  $\mu$ m<sup>2</sup> and 245 x 245  $\mu$ m<sup>2</sup>, respectively.

Figure II-3. Chip photograph of the LNA (Size : 0.43 x 1.20 mm<sup>2</sup> including pads).

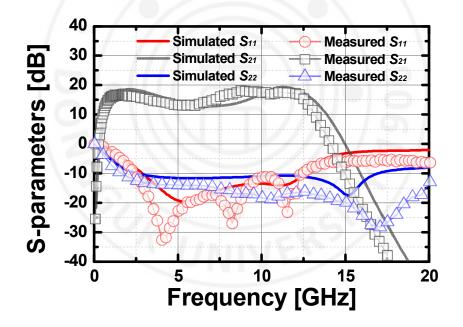

Figure II-4. Measured and simulated results of S-parameters for the LNA.

## 2.3. Measurement results

The proposed LNA was implemented with 65 nm RF-CMOS. As shown in Figure II-3, the overall chip area for the UWB LNA is  $0.43 \times 1.20 \text{ mm}^2$ . The power consumption of the LNA is 14.92 mW from a 1.2 V supply.

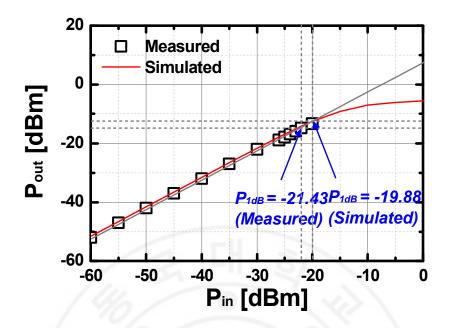

Figure II-5. Measured and simulated results of P1dB for the LNA at 6 GHz.

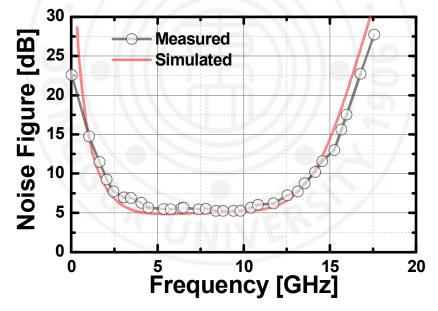

Figure II-6. Measured and simulated results of NF for the LNA.

On-chip measurements of the phase linearity (group delay variation) and Sparameters of the LNA were carried out by Keysight N5224A PNA. Figure II-4 shows the measured and simulated S-parameters. Within 1 - 13 GHz, the measured maximum value of S<sub>21</sub> is 18.21 dB at 8.75 GHz, and the minimum value of it is 13.12

Figure II-7. Measured and simulated results of group delay for the LNA.

dB at 6 GHz. In this frequency range, the measured input and output return-loss are better than 10 dB, and the measured 3-dB bandwidth of the power gain is wider than 12 GHz. The measured results correspond well with the simulation, as illustrated in Figure II-4. As can be seen the Figure II-5, the input-referred 1 dB compression point (IP<sub>1dB</sub>) was measured by gradually increasing the input power level at 11 GHz, and the result depicts -21.43 dBm of IP<sub>1dB</sub>. The noise figure measurement was performed with Agilent N8975A noise figure analyzer. The measured and simulated noise figures of the LNA are shown in Figure II-6. The minimum NF is 5.28 dB at 9.4 GHz. The measured and simulated group delay of the implemented amplifier are presented in Figure II-7. In the range of 3 - 11 GHz, the measured group delay variation is 101 psec at 5.1 GHz (165 psec at 10.6 GHz) and the group delay variation is around  $\pm 31$  psec.

So as to assess the performance of the proposed LNA, the figure-of-merit (FOM) is given by [35]:

$$FOM\left[\frac{GHz}{mW}\right] = \frac{\left|S_{21}\right|\left[dB\right] \times BW[GHz]}{\left|NF - 1\right|\left[dB\right] \times Power_{DC}[mW]}$$

(2-3)

| LNA                                    | This work | [32]       | [33]   | [34]       |  |

|----------------------------------------|-----------|------------|--------|------------|--|

| Tech. [nm]                             | 65        | 180        | 130    | 90         |  |

| Freq. [GHz]                            | 1 - 13    | 3.1 - 10.6 | 2-9.6  | 3.1 - 10.6 |  |

| $G_{MAX}$ [dB]                         | 18.21     | 12.26      | 11     | 22.6       |  |

| $S_{II}$ [dB]                          | < -10     | < -11.8    | < -8.3 | < -10.5    |  |

| NF <sub>min</sub> [dB]                 | 5.28      | 4.24       | 3.6    | 5.5        |  |

| IP <sub>1dB</sub> [dBm]                | -21.43    | -22        | -16.5  | -19.7      |  |

| <i>Group delay</i><br>variation [psec] | 134±31    | 90.9±29.8  | NA     | 73±41      |  |

| $P_{DC} [mW]$                          | 14.92     | 10.34      | 19     | 34.8       |  |

| FOM                                    | 3.42      | 2.74       | 1.69   | 1.08       |  |

Table II-1. Summary of the proposed LNA and comparison with previously published CMOS LNAs.

Table II-1 contrasts the performance summary for the implemented transformerbased UWB LNA with previously reported CMOS wideband LNAs. The proposed LNA accomplishes better FOM than references in [32-34].

## III. Compact I/Q Up-Conversion Chain for a 5G Wireless Transmitter

#### 3.1. Introduction

The emerging fifth-generation wireless standard (5G) in the millimeter-wave regime is aimed at achieving higher speed data transmission and higher capacity with high-quality communication. Recently, a prototype system for 5G mobile communications using the millimeter-wave band has been successfully demonstrated [36-37].

In CMOS wireless transceiver, the direct-conversion architecture is widely used for mobile communication since not only can it be miniaturized, it can also reduce power consumption compared to heterodyne architecture [38-39]. However, in implementing a highly integrated millimeter-wave transceiver with multiple channels, the superheterodyne architecture is more reliable [37]. Specifically, the intermediate frequency (IF) upconverter should be carefully designed with a suppressed in-phase/quadrature (I/Q) mismatch, and it has to provide high linearity. A variety of studies have reported the improvement of the linearity of a CMOS upconverter, such as voltage feedback with adaptive biasing schemes [40], and a resistive feedback network with inter-stage inductor [38], but these approaches consume a large amount of chip area. In [39], a complementary derivative superposition technique [41] was applied to achieve high linearity. However, the reported quadrature signal generator (QSG) occupies most of the chip area, which is inappropriate for a 5G wireless transceiver with integrated multifunctional blocks.

Figure III-1. A block diagram and the specifications of the proposed up-conversion mixer for a 5G wireless transmitter [37]. The mixer consists of a quadrature signal generator and a Tx up-conversion chain [42].

#### 3.2. Design of the I/Q Upconverter

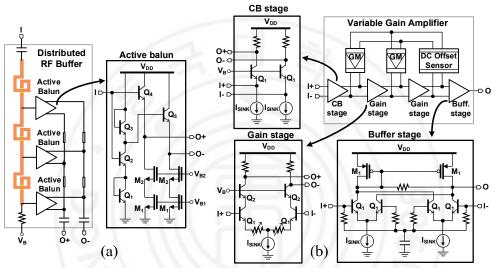

A block diagram of the designed I/Q upconverter with a QSG is presented in Figure III-1 [42]. The designed Tx up-conversion chain consists of an intermediate frequency (IF) amplifier, an I/Q double-balanced passive mixer for low flicker noise [45], a current-mode GM stage with a cascode amplifier, variable resistor and digital capacitor-bank for tuning the center frequency, and a transformer-based balun for single-ended output. A negative gm (NGM) cell implemented with a cross-coupled pair is connected in parallel with the output of the GM stage, which operates in a weak inversion to cancel the 2nd derivative of g<sub>m</sub> which mainly contributes to IM3 in the GM stage [43-44]. A super-source follower which has local feedback through M3 (Figure III-2 (d)) is used to drive the low IF input resistance of the passive mixer, and it provides a high load impedance to the variable gain amplifier in voltage mode at the baseband. The double-balanced passive mixer shown in Figure III-2(e) is employed to perform an up-conversion with high linearity and low-flicker noise. The

Figure III-2. Schematics of the (a) active balun, (b) unit-cells for the LO driver and buffer, (c) CML latch, (d) IF amplifier, and (e) double-balanced passive mixer.

double-balanced mixer can also improve both LO-to-IF and IM2 performance owing to its balanced structure. By utilizing rail-to-rail LO signals with 25% of the duty cycle from the QSG, a 3dB higher gain can be obtained with smaller nonlinearity and noise contribution from the mixer compared with when using 50% of the duty cycle [46]. The up-converted I and Q signals from each mixer are combined in current mode through the GM stage with cascode devices, as shown in Figure III-3.

The QSG with a 25% duty cycle consists of an active balun, a 3-stage CLK driver, a frequency divider implemented with two CML D-latches, and a 4-stage LO driver.

Figure III-3. Schematic of the GM and NGM stages. It is noteworthy that the IM3 of the up-converted signal can be improved through the NGM stage.

It converts the single-ended 2fLO signal to the 25% duty cycle I/Q ( $0^{\circ}/90^{\circ}/180^{\circ}/270^{\circ}$ ) signals used for the LO driving signals of the passive mixer. To generate a differential output signal from a single-ended sinusoidal CLK signal of -10dBm, an active balun is implemented using common gate and common source stages in parallel, as shown in Figure III-2(a). Since the size of the active balun is only 65µm<sup>2</sup>, it can consume less chip area than passive balun (> 180µm<sup>2</sup> at 20GHz). The rail-to-rail output voltage swing of the active balun is achieved by using the CLK driver consisting of three-stage self-biased inverters, as shown in Figure III-2(b). A shunt inductor of 650pH is placed to compensate for part of the loading capacitance for driving the loading capacitance from the CML D-latches. Since an I/Q mismatch of the LO signal generated by the QSG directly affects the error vector magnitude performance of the transmitter, the required gain and phase mismatch in the upconverter should be less than 0.5dB and 3°, respectively [47]. It can be seen that

the QSG with the frequency divider with two high-speed D-latches with inductive peaking combined with the cascaded self-biased inverters is a quite appealing approach to meet the gain and phase error requirements while occupying a relatively compact area. Finally, the output I and Q signals generated by the frequency divider are amplified to provide rail-to-rail swing to the LO of the double-balanced mixer using the LO buffer, as presented in Figure III-2(b).

Figure III-4. A photograph of the chip with the proposed up-conversion mixer with the QSG (chip size:  $0.58 \times 0.98$ mm<sup>2</sup>).

Figure III-5. Measured and simulated S<sub>11</sub> for LO<sub>IN</sub>.

## 3.3. Measurement results

The proposed Tx upconverter was implemented with a 65-nm CMOS process. Figure III-4 presents a microphotograph of the chip of the I and Q upconverter block (the chip occupies  $0.58 \times 0.98$ mm<sup>2</sup>). The implemented up-conversion chain

Figure III-7. Measured up-converted RF output results with and without the NGM stage.

consumed 48.7mW (QSG: 24.3mW, Up-mixer chain: 24.4mW) from a 1V supply, and digitally controlled through a serial-peripheral-interface (SPI) scan-chain.

On-chip measurements of the S-parameters were performed with E8361C PNA network analyzer, the conversion gain and output third-order intercept point (OIP3) measurements were performed with a Keysight N9030A PXA spectrum analyzer, a

Figure III-8. Measured RF output, LO leakage, and image with a single-tone input signal.

Figure III-9. Measured up-converted RF output results for the I/Q channels with less than 0.2dB of gain mismatch.

Keysight E8257D analog signal generator for the LO signal, and a Rohde & Schwarz SMW200A vector signal generator for the differential I/Q baseband signals. Figures III-5 and III-6 show the measured S-parameters which corresponded well with the simulation. Figure III-7 presents a comparison of the measured output spectrum with two-tone IF inputs of 100Mz and 110MHz with and without activating the NGM cell, the measured OIP3 with NGM was 14.45dBm while the OIP3 without NGM was

Figure III-10. Phase mismatch based on the measured gain mismatch and IRR contour. The phase mismatch was expected to be lower than 0.5degrees.

Figure III-11. Measured and simulated results of gain and RF power for the implemented upconverter depending on IF power with  $f_{IF} = 300Mz$  and  $f_{LO} = 22.4GHz$ .

only 11.87dBm, which shows +2.58dB of improvement owing to the 3rd harmonic cancellation with a negligible extra power consumption of  $438\mu$ W. On the other hand, when the NGM is turned on, the insertion-loss is lower than 1dB. For the measurement of the image rejection ratio (IRR), a single-tone IF input with a frequency of 300MHz was applied at the IF input port of the mixer. As shown in Figure III-8, the measured LO leakage and IRR were -37.7dBc and -46.9dBc,

| Reference             | This work | [38]    | [39]      | [40]        |  |

|-----------------------|-----------|---------|-----------|-------------|--|

| Technology            | 65nm      | 65nm    | 65nm      | 0.13µm      |  |

| LO Freq. [GHz]        | 20~23     | 51 ~ 69 | 28        | 18.9 ~ 29   |  |

| RF Freq. [GHz]        | 10~11.5   | 60      | 27.6~28.4 | 23.4 ~ 29.2 |  |

| P <sub>LO</sub> [dBm] | -10       | 0       | -13       | 0           |  |

| Gain                  | 9.12      | 6.2     | 11.4      | -1.9        |  |

| $OP_{1dB} [dBm]$      | 2.65      | -7.3    | 2         | 0.3         |  |

| OIP3 [dBm]            | 14.45     | N/A     | 15.7      | N/A         |  |

| Chip area [mm2]       | 0.57**    | 0.42*   | 1.23**    | 0.86***     |  |

| $P_{DC} [mW]$         | 48.7**    | 17.8*   | 15*       | 39.3***     |  |

Table III-1. Comparison with previously reported up-conversion mixers.

\* Mixer only, \*\* Mixer with quadrature signal generator, \*\*\* Mixer with LO buffer

respectively. Figure III-9 shows the measured gain mismatch of I/Q channels by varying LO frequency for a fixed IF frequency ( $P_{IF}$ =-30dBm at  $f_{IF}$  = 300MHz), which was lower than 0.2dB. Based on the measured gain mismatch and IRR, we expect that the phase mismatch for the mixer was lower than 0.5degrees (Figure III-10). The measured gain and output power depending on IF input power closely matched the simulation results, as presented in Figure III-11. Table III-1 compares the implemented mixer with previously reported up-conversion mixers [38-40]. The designed mixer with quadrature signal generator in the upconverter showed the smallest chip size.

# IV. 2–18 GHz Compressed Sensing Receiver with Broadband LO Chain

#### 4.1. Introduction

Good control and analysis of the spectrum are important in applications for protection and defense. The traditional method, based on the Nyquist sampling principle, allows an ultra-fast analog-to-digital converter (ADC) with a sampling frequency greater than twice the average frequency of the transmitted signal to track an unseen signal in real time. While more than 10 Gb/s, or even better, interleaved ADCs have recently been proposed as Integrated Circuits (ICs) [14], the ultra-fast back-end module for microwave signal monitoring still needs tens of watts of power, and its size is considerably voluminous. It is therefore very challenging to implement a microwave sensing receiver which collects and processes unidentified signals with the Nyquist sampling rate in real time. The airborne surveillance systems in particular need miniaturized microwave monitoring receivers with low power consumption [15], [48].

Recently, a compressed sensing receiver capable of real-time signal restoration was introduced as an excellent solution to avoid the above-mentioned problems by obtaining a very high compression ratio between the Nyquist rate and the ADC sampling rate at the back-end. In [48]–[51], researches for the compressed sensing architecture have been carried out. It can be possible the reconstruction of the signal even with a sub-Nyquist sampling frequency using a random sensing matrix that satisfies the requirement of the restricted isometry property (RIP) [53] when the input signal is sparse. The pseudo-random bit sequence (PRBS) signal [52-53], is the most commonly employed sensing array.

Based on the proven compressed sensing theory several compressed sensing receivers (CSRXs) were published in the literature [48-50] to track broadband RF signals in real time. However, the realization of a microwave CSRX with the broadband PRBS generation and the high-swing local-oscillator (LO) signal transmission to the down-converting mixer without severe spectrum distortion of the PRBS signal is challenging.

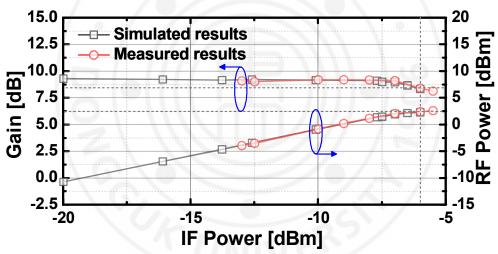

Figure IV-1. A block diagram of the integrated 4-channel compressed sensing receiver in a 0.13-µm BiCMOS [54].

Figure IV-2. Schematics of (a) the distributed RF buffer and (b) the variable gain amplifier [54].

## 4.2. The compressed sensing receiver design

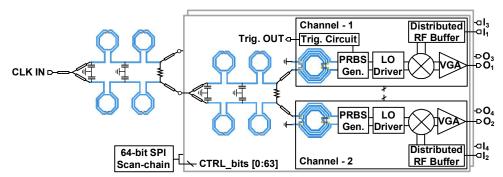

In order to support the improved compression ratio, four independent receiving channels with a 36-Gb/s PRBS generator having a band-equalized LO chain are integrated to the CSRX, as shown in Figure IV-1 [54].

A 2–18 GHz distributed amplifier configured with three active balun cells, a four-stage variable gain amplifier (VGA), and a double-balanced passive mixer are included in the broadband receiver. The passive mixer is driven by the active balun, which transforms the single-ended input to the balanced output in the current mode. As shown in Figure IV-2(a), in order to the characteristic impedance  $Z_0 = 50 \Omega$  over 2–18 GHz at the RF input, a distributed LC network is constructed as the pseudo-transmission line.

Figure IV-3. Block diagram of PRBS generator.

The intermediate frequency (IF) signal in the range of 100 kHz to 500 MHz is amplified by the VGA from the IF port of the mixer. For the low input impedance and the improved linearity, the first stage for the VGA is the common base, which makes the mixed IF current to easily deliver to the VGA, as shown in Figure IV-2(b). The cascode amplifiers are used in the 2nd and 3rd gain stages. To change the variable gain, the source degenerated resistors and the variable 4-bit resistor-bank are implemented in each of these. So as to drive the external back-end block through the 50- $\Omega$  CPW on the PCB, the output buffer is realized.

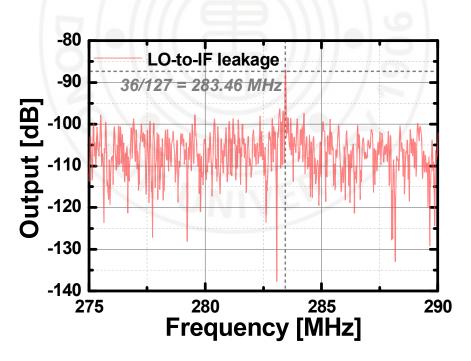

Since the PRBS LO signal is composed of multiple sets of tones which extend even into the IF band, the LO-to-IF isolation is most critical issues in the CSRX design. Thus, the double-balanced mixer is built to obtain high isolation between the mixer's LO and IF ports by canceling out the balanced LO leakages at the mixer's IF port where the lowest LO tone is 280 MHz.

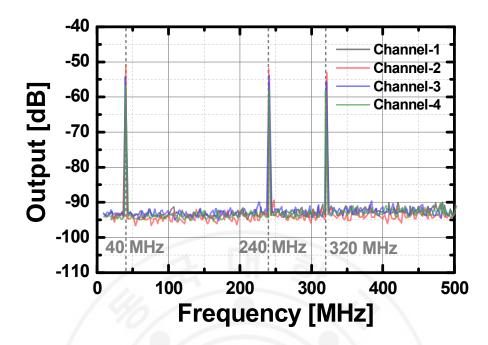

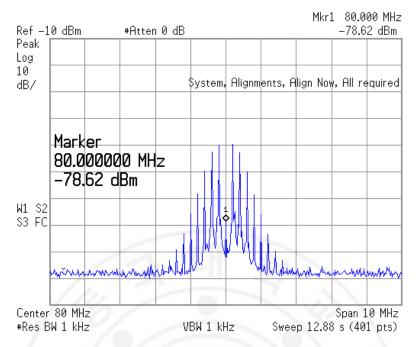

As the sensing matrix of each CSRX channel, a 36-Gb/s PRBS generator with half-rate 36-Gb/s PRBS signal, which is integrated as the LO mixing signal, was introduced. In order to implement the 36-Gb/s PRBS generator, an interleaved linear-feedback shift register (LFSR), two XORs, and a 2:1 multiplexer (MUX) by using the "cycle-and-add" nature of the m-sequence signal [56] are integrated, as shown in Figure IV-3. The 36–Gb/s  $2^7$ -1 PRBS can be generated by seven consecutive flip-flops with a half-rate clock (CLK) frequency of 18 GHz coming from the CLK distribution network. According to the characteristic polynomial x7+x6+1, the designed architecture generates L = 127 of the sequential length. In the Fibonacci LFSR, an XOR play a role in the feedback circuit. Taps (3,6), (0, 6), (2, 6), and (5, 6) are used as the input for the channel-1, channel-2, channel-3, and channel-4 PRBS patterns, respectively. So as to provide f<sub>clk</sub> = 18 GHz to each channel evenly, three lumped-element Wilkinson dividers are integrated in the CSRX. All the variables are digitally controlled by using a 64-bit serial-peripheral-interface (SPI) scan-chain.

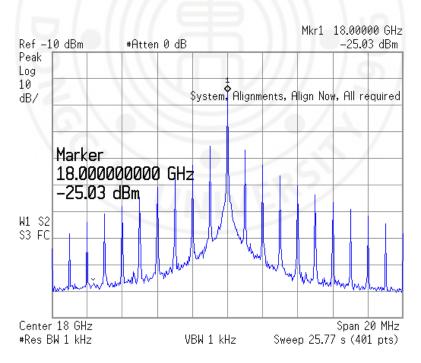

The spectrum of the PRBS (m-sequence) signal is made up of an abundant amount of harmonic tones of  $f_p = f_{PRBS}/L = 280$  MHz resulting in a broadband sincshaped spectrum. Thus, the 36-Gb/s PRBS generator's the high-frequency spectrum

Figure IV-4. (a) A block diagram and the frequency response of the band-equalized LO generator and simulated PRBS pattern and (b) a schematic of the LO driver.

with the 2:1 MUX is specifically influenced by the the LO driving chain having a low-pass response and frequency response of the MUX due to parasitic capacitances. As a results, it can be difficult to achieve successfully compressed sensing caused by the severely distorted high-frequency harmonic tones from the PRBS generator. In order to solve this problem, a feedback amplifier is designed to provide a broadband input matching and the gain peaking at the designated high-frequency region as well as to equalize the high-frequency response of the LO signal after the 2:1 MUX of the PRBS generator, as shown in Figure IV-4(b). A shunt-shunt feedback network is constructed with  $Q_2$ ,  $R_1$ ,  $R_2$ , and  $R_3$ . The peaking of the frequency response can be controlled by the ratio of  $R_1/R_2$  and  $R_3/R_2$  [57]. Figure IV-4(a) shows the simulated PRBS pattern at the LO port of the mixer as well as at the input and output of the 2:1 MUX.

Figure IV-5. A microphotograph of the implemented 4-channel CSRX chip (chip size =  $2.9 \times 4.45 \text{ mm}^2$ )

Figure IV-6. The PCB of the packaged CSRX chip for the measurement.

## 4.3. Measurement results

With  $f_T = 230$  GHz, the CSRX was realized in STMicroelectronics 0.13-µm BiCMOS process. A chip photograph of the implemented four-channel CSRX is shown in Figure IV-5. The area of the fabricated chip is  $2.9 \times 4.45$  mm<sup>2</sup>. The packaged CSRX chip on the PCB is depicted in Figure IV-6. The measured results

Figure IV-7. Measured and simulated  $S_{11}$  results for the CLK and RF inputs in the CSRX.

Figure IV-8. Measured LO-to-IF leakage at 18 GHz CLK input.

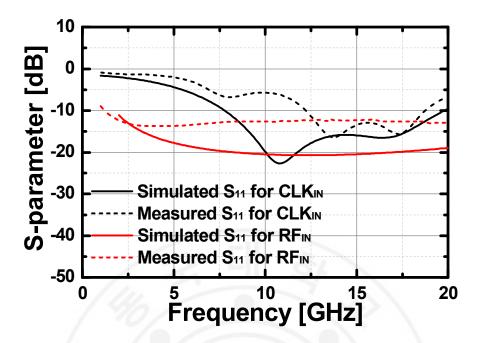

for  $S_{11}$  of the LO CLK and RF input are shown in Figure IV-7. The return loss of the CLK input port was around 15 dB at  $f_{clk}=18$ GHz, and that of the RF input port was

Figure IV-9. Measured IF output at 40 MHz, 240 MHz, and 320 MHz with a single tone input at  $f_{RF}$  =2 GHz for four independent CSRX channels.

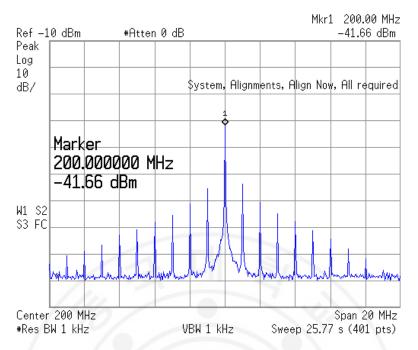

Figure IV-10. Spectra of the 18 GHz RF input signal (FM with a pulse signal).

better than 10 dB over the aimed 2-18 GHz range. As shown in Figure IV-8, the measured LO-to-IF leakage was around 90 dB.

Figure IV-11. One of the sensed repetitive IF signal of the FM input at 18 GHz with a pulse signal in the CSRX.

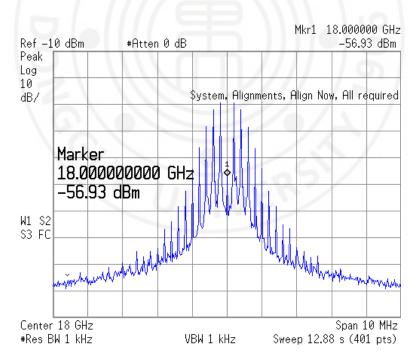

Figure IV-12. . Spectra of the 18 GHz RF input signal (FM with a ramp signal).

A sinusoidal input signal with  $f_{RF} = 2$  GHz using an Agilent 83623B signal generator is firstly applied to verify the microwave compressed sensing. In order to

Figure IV-13. One of the sensed repetitive IF signal of the FM input at 18 GHz with a ramp signal in the CSRX.

| spectrum sensors.    |             |                           |             |           |  |  |  |

|----------------------|-------------|---------------------------|-------------|-----------|--|--|--|